### Plan for new device's R&D using Versal for the experiments at KEK

Yun-Tsung Lai

**KEK IPNS**

ytlai@post.kek.jp

Workshop on Realtime Machine Learning

11<sup>th</sup> Apr., 2024

### Outline

- Application of FPGA in HEP experiments

- DAQ, L1 Trigger, HLT systems

- Versal project @ KEK IPNS, Collider Electronic Forum:

- Introduction & Overview

- Progress on functionality study: PAM4, PCIe, AI engine, DPU

- HLS and ML inference study plan

- Algorithm implementation

- Summary & To do

## Application of FPGA in HEP experiments

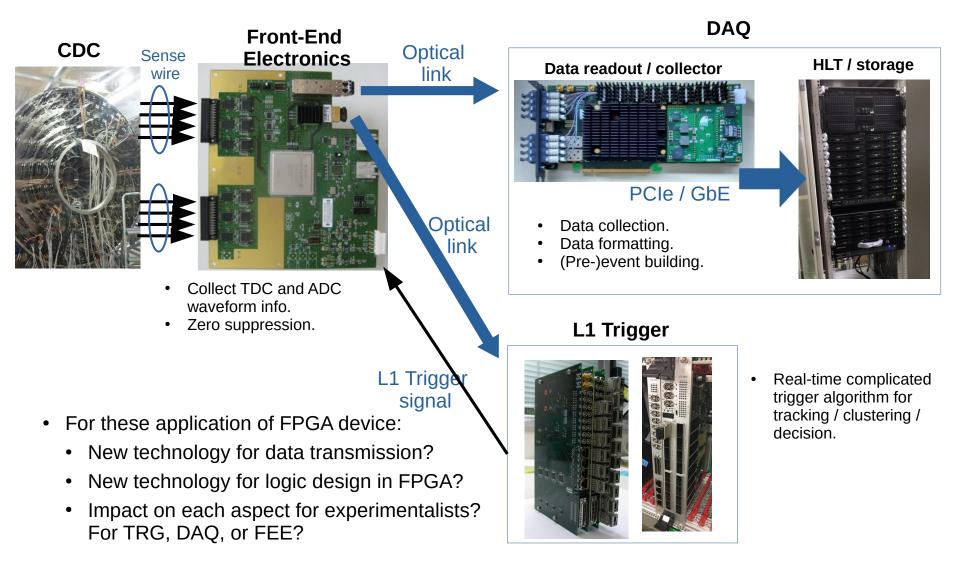

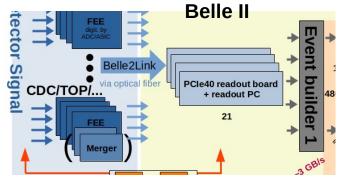

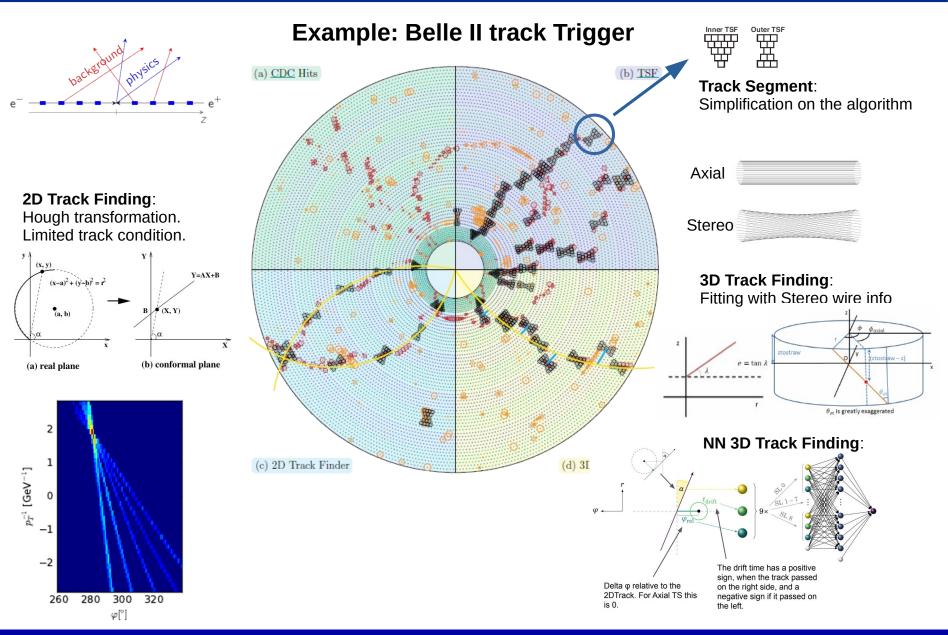

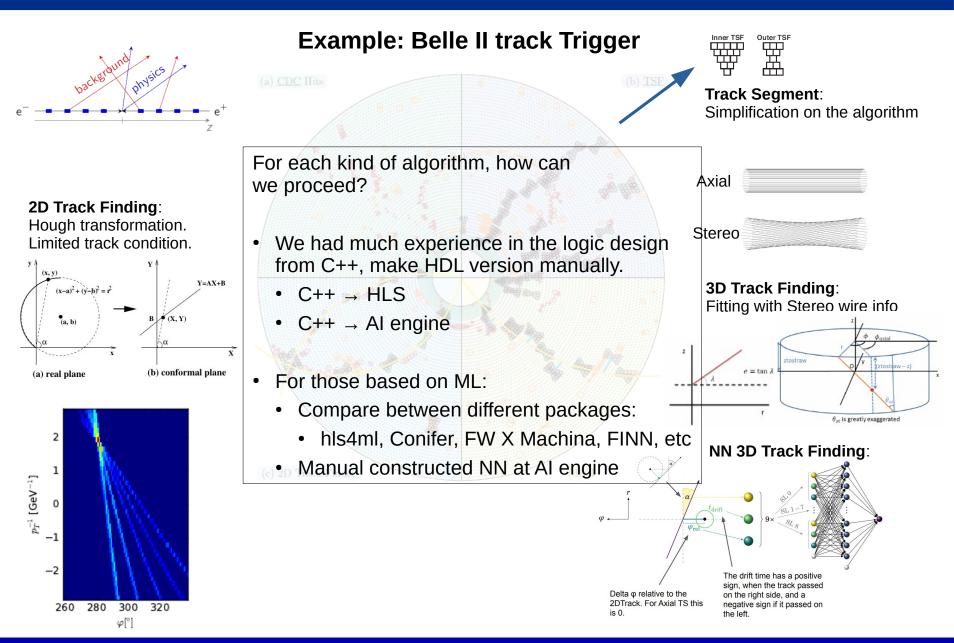

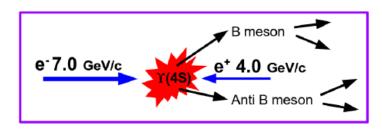

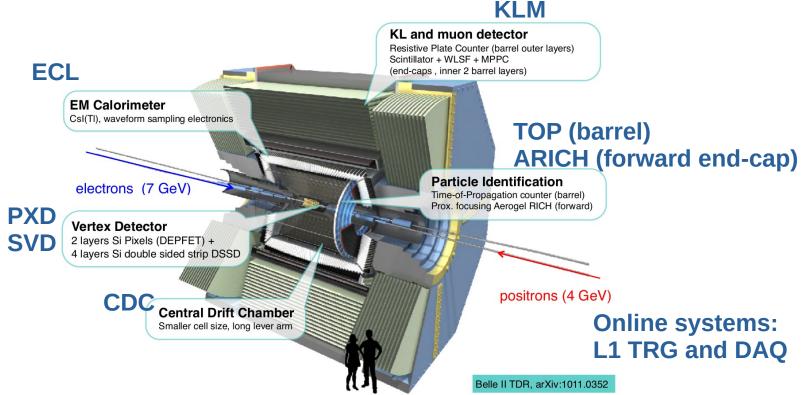

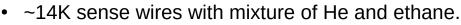

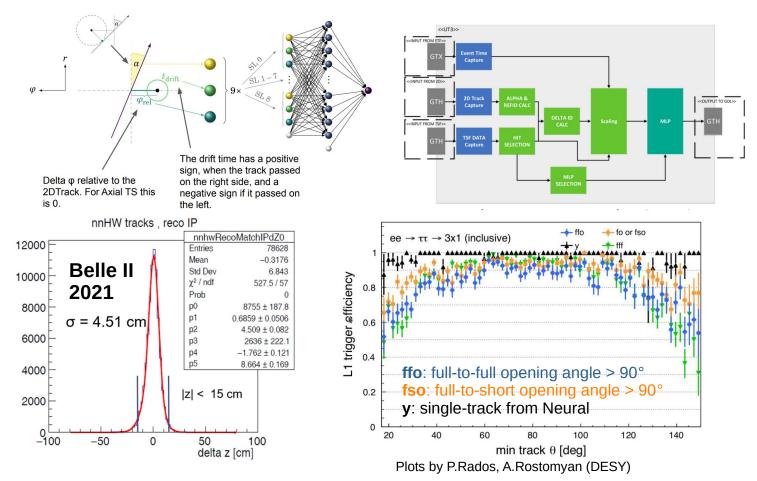

• Here we use Belle II Central Drift Chamber (CDC) as an example.

## Application of FPGA in HEP experiments (cont'd)

**Data Link**

**Data Link**

**FPGA**

(FEE)

• Hardware acceleration:

**High-level**

- Not only CPU, but also GPU and FPGA.

- Acceleration on softwarebased calculation.

- FPGA FPGA transmission:

- Optical link with FPGA MGT and optical modules.

- Non-Return-to-Zero (NRZ).

- Different encoding based on protocol design purposes.

e.g. 8B/10B and 64B/66B.

- <10 Gbps for DAQ.

- <25 Gbps for TRG.

- Strong FPGA devices with:

- Larger number of cells.

- Larger data bandwidth.

are critical for the usage in:

- **TRG**: complicated algorithm implementation.

- **DAQ**: collect and process large data.

**FPGA**

(Trigger)

**FPGA**

(Readout)

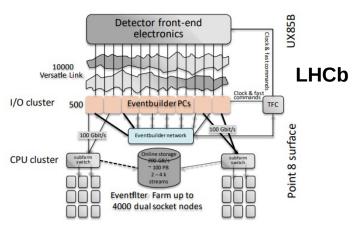

- **FPGA server transmission:**

- Data transmission and system slow control.

- GbE, PCI-express, VME, etc.

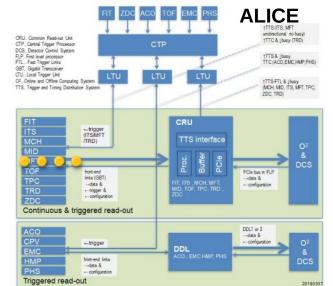

- PCI-Express is the most popular one nowadays: PCIe40 in ALICE, LHCb, and Belle II.

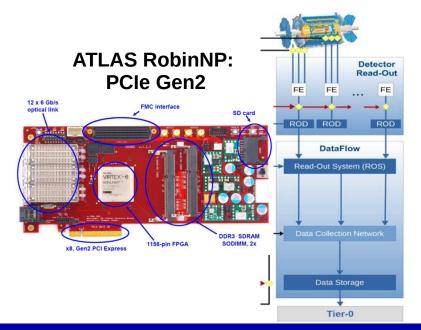

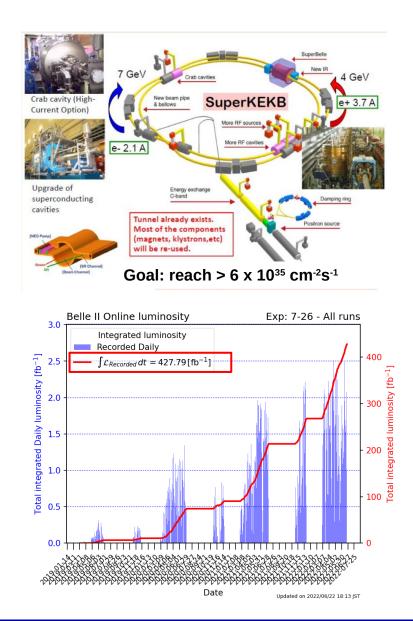

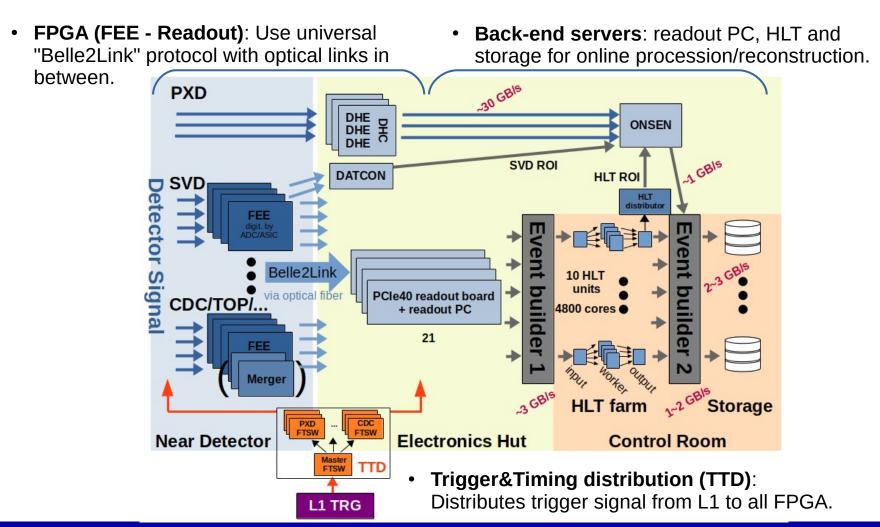

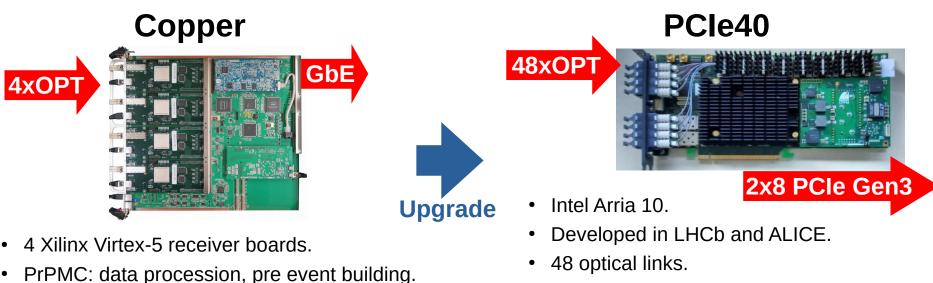

## DAQ system

Readout: PCIe has been the most popular solution for electronics → server interface.

### PCIe40: PCIe Gen3

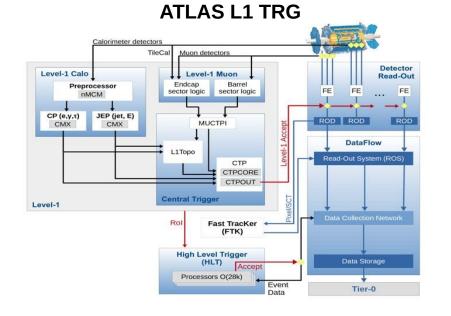

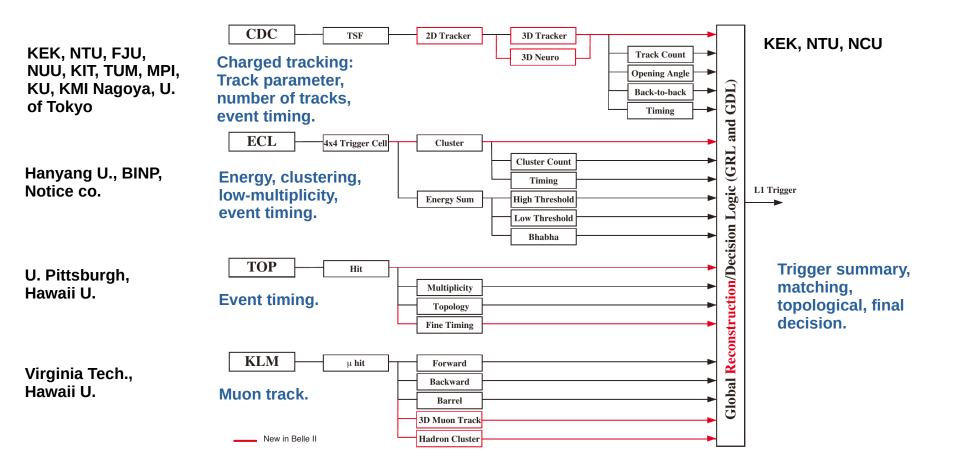

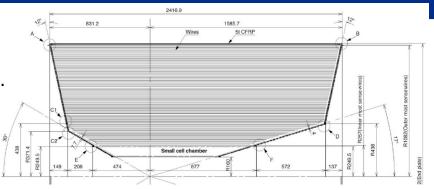

## L1 Trigger system

- Provide L1 trigger signal to DAQ using FPGA chips for real-time processing on detector raw data.

- Reason for L1: Buffer storage are not enough for all data due to high event rate and short bunch spacing in collider experiment.

#### Yun-Tsung Lai (KEK IPNS) @ Workshop on Realtime ML

6: 40 10 7: 44 11 8: 48 12

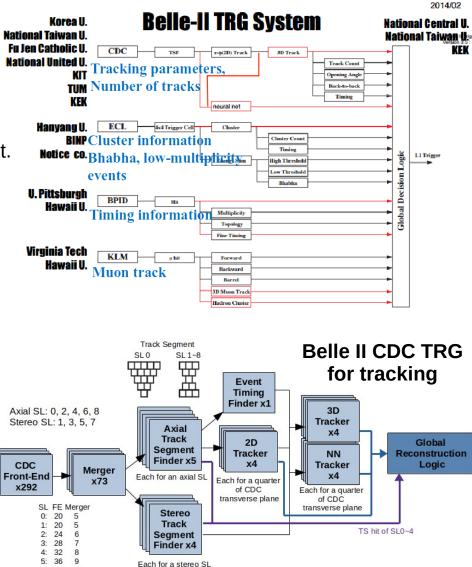

### Trigger device for Belle II and ATLAS

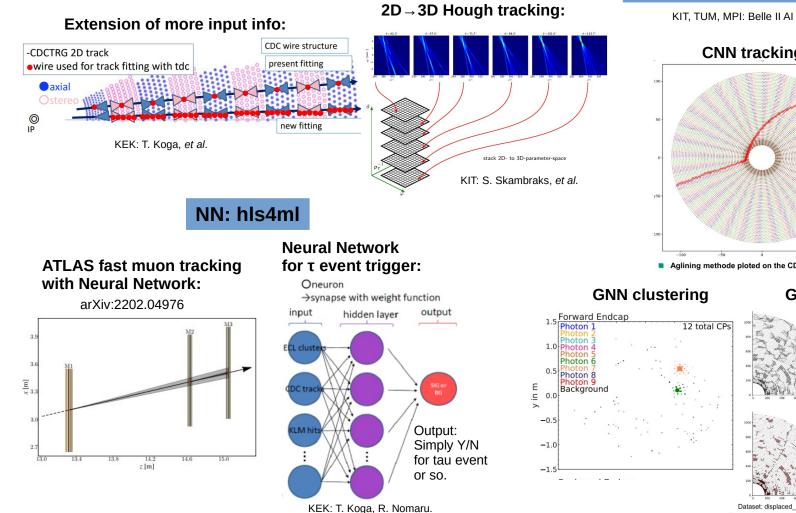

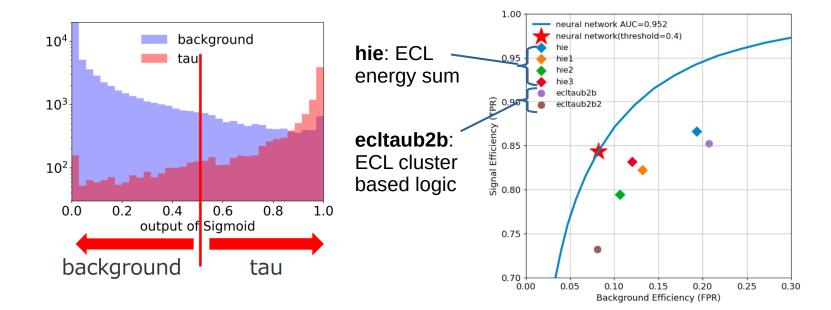

- For TRG purpose, complicated algorithm is implemented to process detector raw data in real-time. Utilization of machine-learning in the logic design became a trend recently.

- Strong FPGA with large resource: improve the logic itself, resolution of triggering, reduce the background rate, and perform everything within a latency limit.

### **Belle II UT3**

### ATLAS Muon Trigger processor

Xilinx Virtex-6 xc6vhx380t, xc6vhx565t 11.2 Gbps with 64B/66B

Xilinx UltraScale XCVU080, XCVU160 25 Gbps with 64B/66B

Xilinx UltraScale+ XCVU13P XCZU5EV GTH,GTY: 16.8 Gbps with 64B/66B

#### 2024/04/11

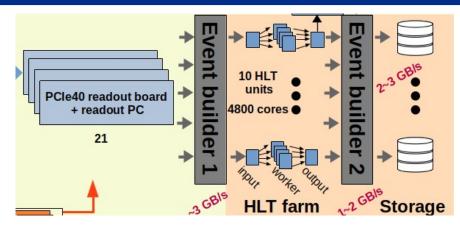

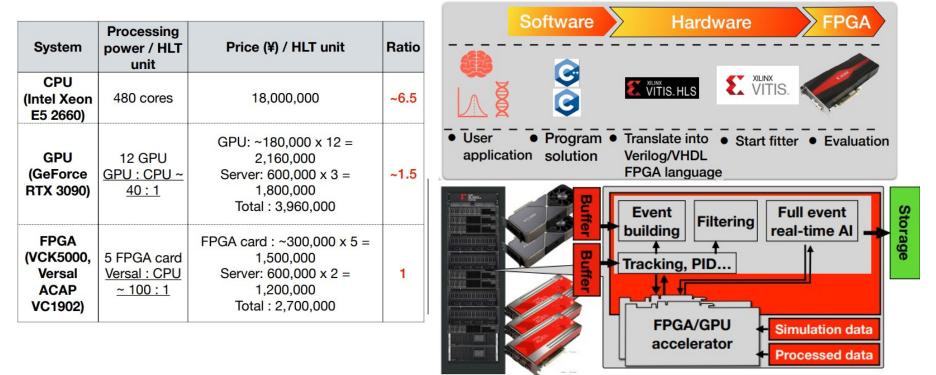

### HLT

- HLT: Computing servers with reconstruction software.

- In Belle II: HLT software = offline software.

- How about the options other than CPU?

- GPU? FPGA for hardware acceleration?

### source: Qi-Dong Zhou, Shandong Univ.

### Versal project @ KEK IPNS

- "Collider Electronics Forum": A new platform for electronics associated technical communication and common device R&D in Japanese HEP community.

- KEK IPNS: E-sys, Belle II, Energy Frontier groups.

- Experiment groups (Belle II, ATLAS, ALICE, nuclear physics) in Japan.

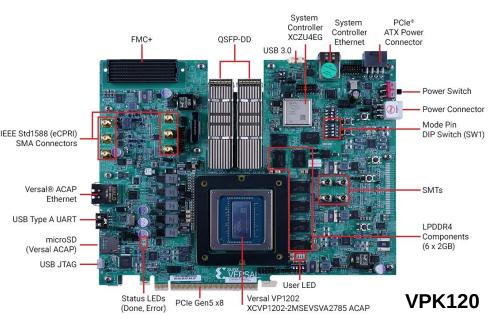

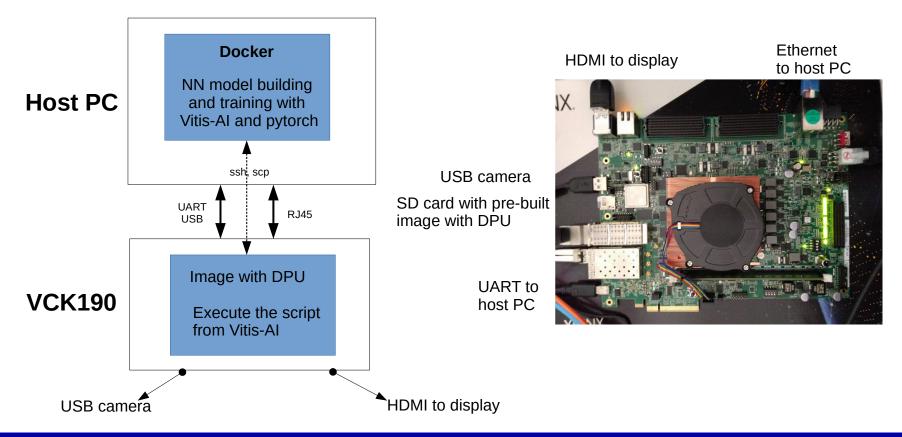

- We purchased a few evaluation kits of the Xilinx Versal series ACAP for joint study.

- Plan: Common and general studies on the new technologies for future electronics device's R&D. Now we plan to use Versal for L1 TRG, DAQ or HLT purpose.

#### 2024/04/11

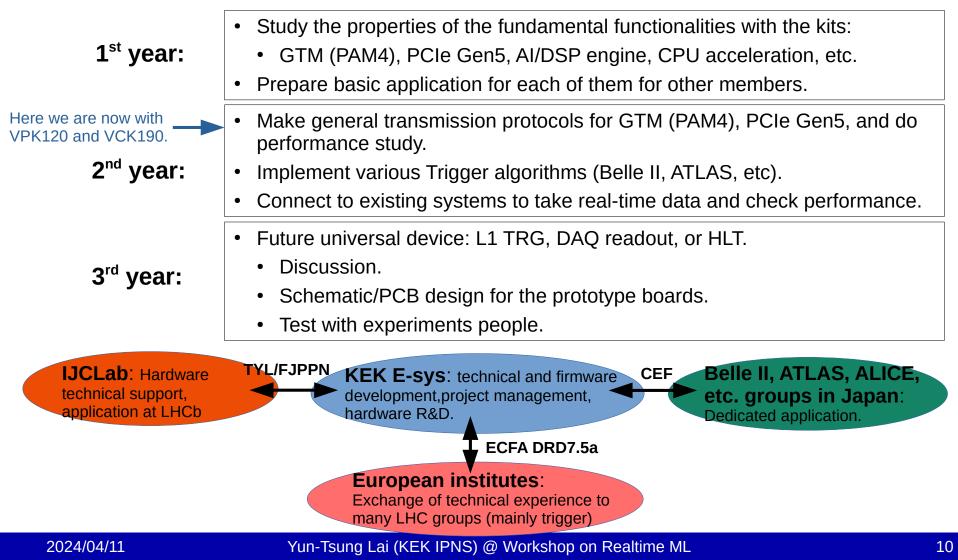

### Versal project: General plan and roadmap

- Our goal: R&D of a new general FPGA device using the Versal ACAP.

- A L1 TRG, DAQ, or HLT device, and also general for different experiments.

- One clear target is UT5 for L1 TRG of both Belle II and ATLAS.

## New technology in Versal FPGA: PAM4, PCIe, AI engine

- Pulse Amplitude Modulation (PAM4):

- Four distinct voltage levels to break through the limit of Non-Return-to-Zero (NRZ), which is ~25 Gbps.

- Using VPK120 to study it.

- Suitable for high-speed link in L1 TRG. Hope to be pioneer to use it in future TRG board.

- PCle Gen5:

- PCIe has been popular option in HEP.

- ALICE, LHCb and Belle II has been using PCIe40 (Gen3).

- Study the properties of newer generation of PCIe is beneficial for the future readout device's development.

- Using VPK120.

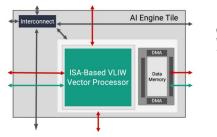

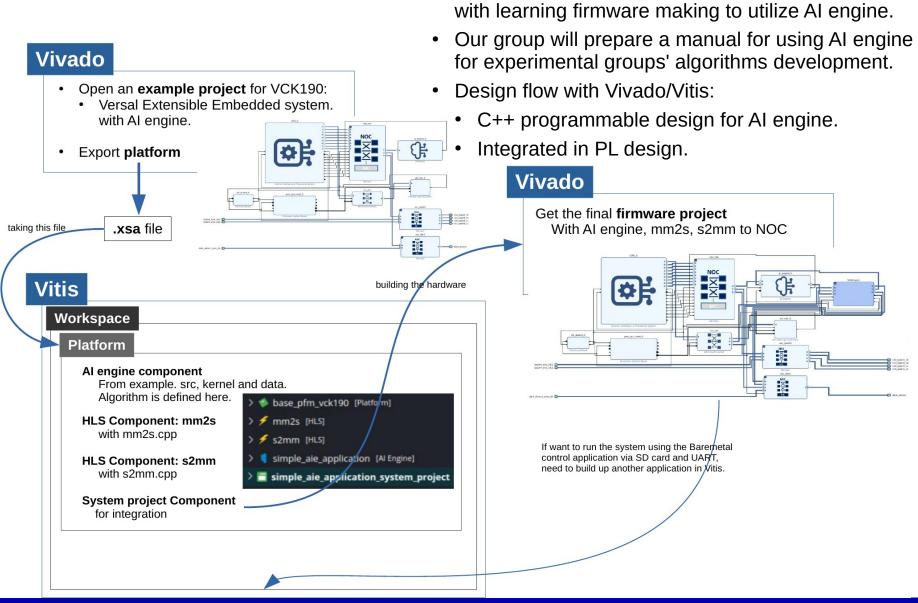

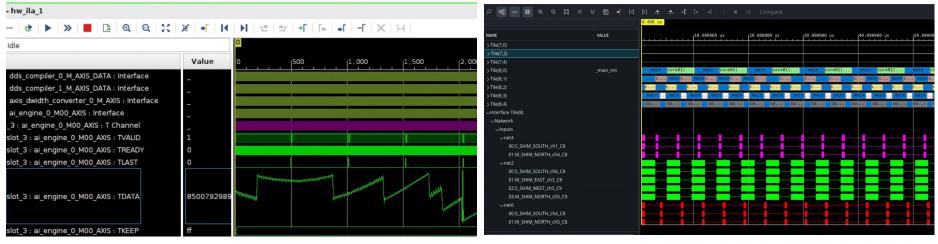

- Al engine: A new technology for data processing.

- Help for our algorithm construction in TRG.

- C programmable.

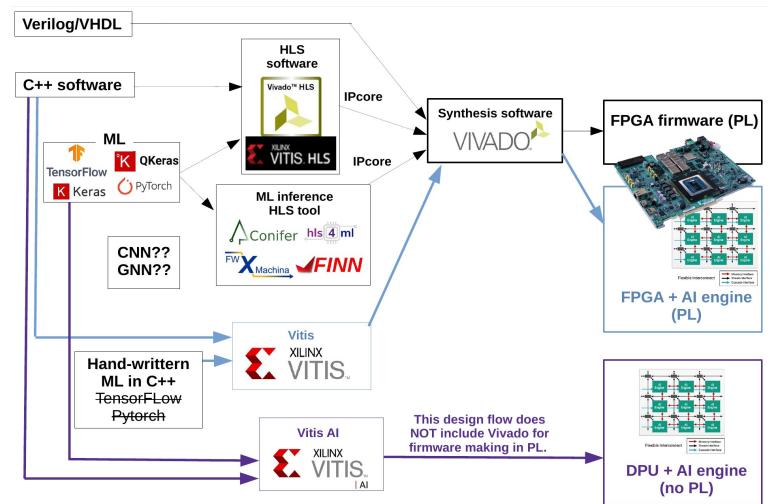

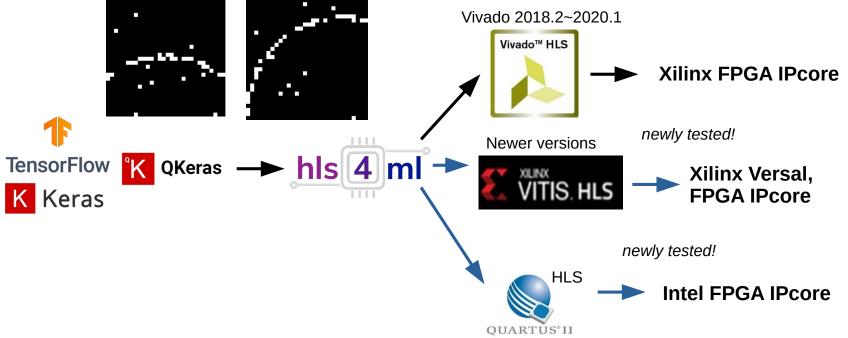

- Together, we study many options of HLS and ML inference in FPGA, and their performance in different TRG algorithms.

- Will use VCK190.

2024/04/11

Limit: ~25 Gbps

PAM4 (Pulse Amplitude Modulation)

Four distinct voltage levels. Two bits per clock cycle.

4 levels

#### 2024/04/11

Yun-Tsung Lai (KEK IPNS) @ Workshop on Realtime ML

## Test bench setup @ KEK E-sys group

- The test bench of VPK120 has been built at E-sys group and released to our members for dedicated studies.

- VCK190 has also arrived at KEK in March. Preparation study is ongoing and will be ready soon.

- Special thanks to Mathis Maurice, internship in E-sys group in 2023 summer, for helping this VPK120 preparation work!

PC side: PCIe Gen5 x16 slot

VPK120 test bench: 2023 summer

PC side: PCIe Gen4 x8 slot

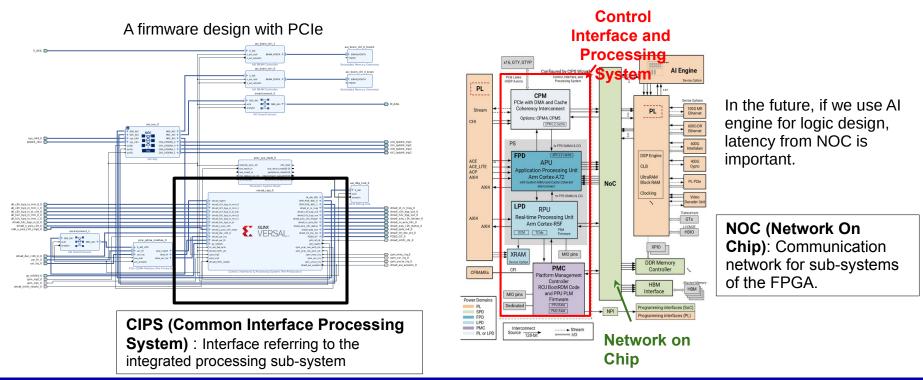

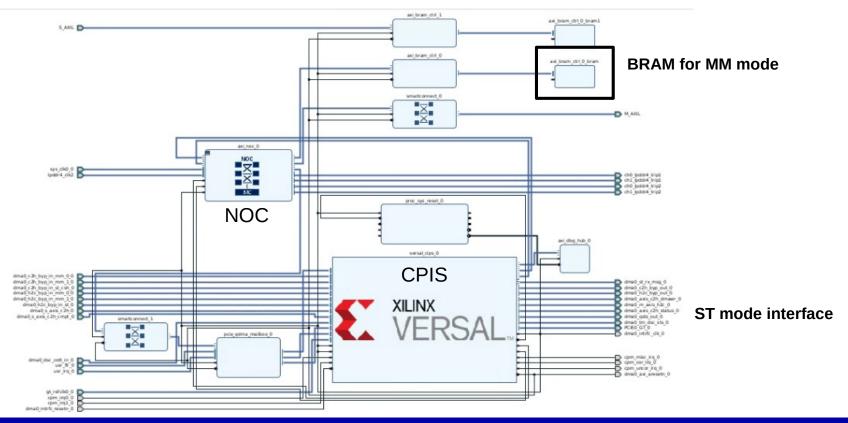

### Firmware making with Versal: PS, CIPS and NOC

- In our experience, FPGA firmware making is:

- Writing HDL codes and using IPcore to control all the **Programmable Logic (PL)**.

- But Versal is an ACAP containing lots of sub-systems together with the FPGA.

- Not only PL, but also **Processor System (PS)**.

- Firmware making tends to rely on the automatic block design rather than the traditional code-writing way.

- For now, we still have limited understanding in PS.

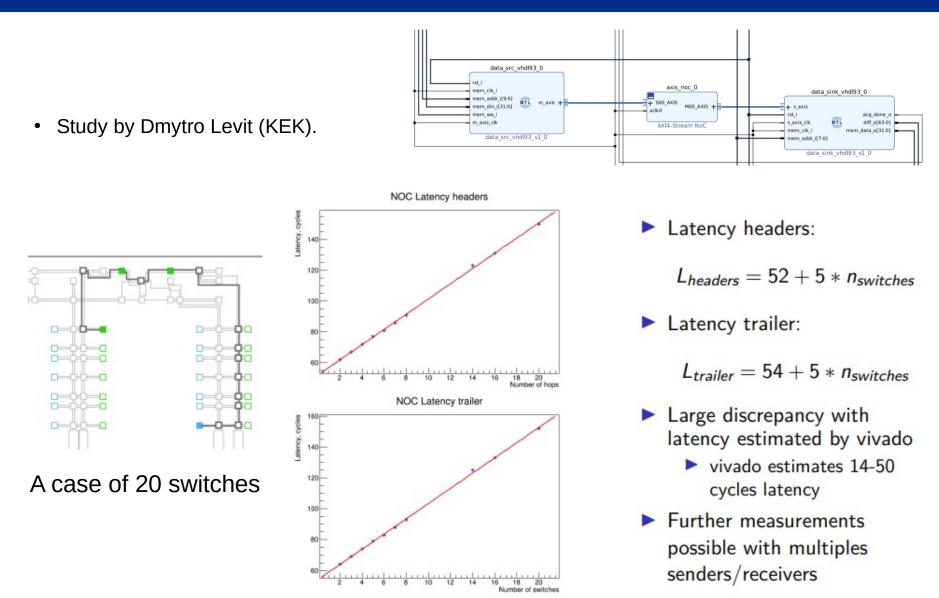

### Latency measurement with NOC

### Versal transceivers: GTYP and GTM

- GTYP: PCIe 5.0 (16) and FMC+ (8)

- 1.25 ~ 32.75 Gb/s.

- Various encoder supported.

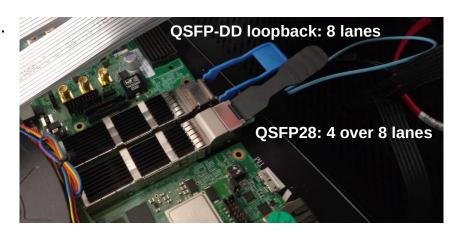

- GTM: QSFP-DD (8\*2)

- NRZ:

- 9.5 ~ 15, 19 ~ 29 Gb/s.

- PAM4:

- 19 ~ 30, 38 ~ 60 Gb/s

- 76 ~ 112 Gb/s: "Half density mode" by combining two lanes.

- No encoding is supported. Need to be make them manually in RTL.

- Our test setup for transceiver study:

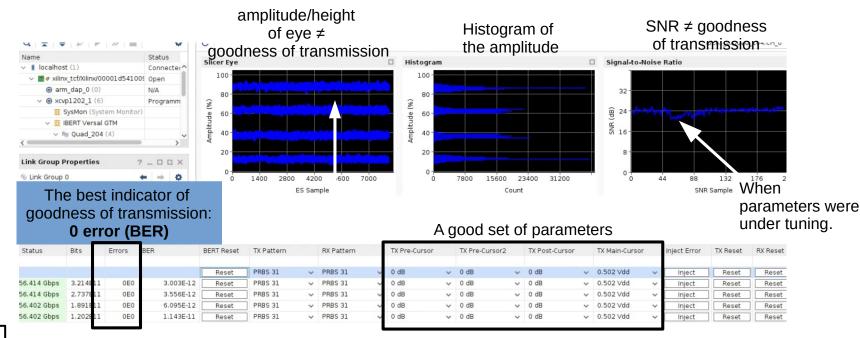

## PAM4 56 Gbps with GTM IBERT, QSFPDD loopback

- PAM4, 56 Gbps per lane. QSFPDD loopback module.

- Parameter tuning on cursor position and termination voltage, etc, is necessary to have stable transmission (0 bit error).

DesignCon 2019 Enabling IBIS-AMI Simulations for Systems Containing PAM4 Retimers at 112Gbps

### Plan

- Further study with realistic QSFPDD module and MPO-16 is ongoing.

- Much higher BER (~10<sup>-6</sup>)

- Forward-Error-Correction will be implemented in our protocol.

- Also other types of PAM4-supported modules: FireFly, etc.

### OSFP-DD-SR8

#### 2024/04/11

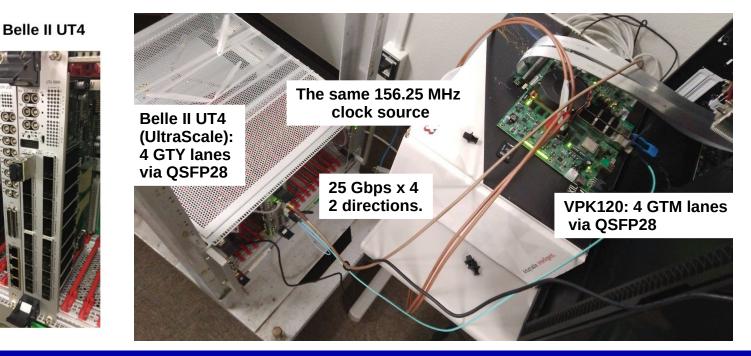

### Protocol development and connection test

- Both 8B/10B and 64B/66B (sync. gearbox) are tested with GTM.

- Raw mode with No encoding: A new generalized protocol has been also made.

- Similar logic to my Belle II TRG protocol design.

- (de)scrambler for DC balance.

- Tested to be stable for both NRZ and PAM4.

- Using this new generalized protocol, connection test (25 Gbps x4, NRZ) between Belle II UT4 and VPK120 has been also tested. Stable in few hours.

- Will test with ATLAS muon board soon.

2024/04/11

### Latency for Versal GTYP and UltraScale(+) GTY

- Latency is a big concern for L1 TRG system.

- Since the beginning of Belle II TRG preparation, we have been studying latency reduction in data links.

- Now we have 25 Gbps running.

- The following are the simulation values from Xilinx website with internal encoder.

- UT4: Virtex UltraScale

- Measured latency in **bold**: Based on the Belle II TRG protocol.

|                      | Raw (UI) | Raw +<br>Async.<br>64B/66B<br>(UI) | 10 (<br>Rav<br>(ns) |            | 10 G<br>64B/<br>(ns)                                              | •        | 25 C<br>Raw<br>(ns) | Sbps,<br>/ |    | Gbps,<br>8/66B |

|----------------------|----------|------------------------------------|---------------------|------------|-------------------------------------------------------------------|----------|---------------------|------------|----|----------------|

| Versal GTYP<br>64/64 | 1127     |                                    |                     | Typi       | cal va                                                            | alue for | 1 lir               | nk in the  | ح  |                |

| Versal GTYP<br>64/32 | 688      |                                    |                     | <b>.</b> . | ical value for 1 link in the<br>nt Belle II TRG: <b>50~100 ns</b> |          |                     |            |    |                |

| UT4 GTY<br>64/64     | 768      | 1458                               | 77                  | 115        | 146                                                               | 147      | 31                  | 33         | 58 | 58             |

| UT4 GTY<br>64/32     | 414      | 990                                | 41                  | 90         | 99                                                                | 122      |                     |            |    |                |

- If we adapt to use Versal GTM: Larger latency will be introduced.

- The following are the max. simulation values from Xilinx website with No encoding.

- Measured latency in **bold**: Based on our generalized protocol.

- For the same setup, latency in term of clock-cycle is basically the same.

- Higher speed is preferred as the processing latency is much smaller.

- In general, latency of GTM is much larger that that of UltraScale(+) GTY or so.

- If we use GTM, just go with PAM4 with > 50 Gbps.

| Versal GTM | Unit Interval<br>(UI) | 10 Gbps<br>(ns) | 25 Gbps<br>(ns) | 56 Gbps<br>(ns) | 106 Gbps<br>(ns) |

|------------|-----------------------|-----------------|-----------------|-----------------|------------------|

| NRZ 64b    | 5833                  | 583 <b>640</b>  | 233 <b>256</b>  |                 |                  |

| NRZ 160b   | 4964                  | 496 <b>730</b>  | 198 <b>237</b>  |                 |                  |

| PAM4 160b  | 2957                  |                 |                 | 53 <b>97</b>    |                  |

| PAM4 256b  | 3233                  |                 |                 | 57 <b>133</b>   |                  |

| PAM4 320b  | 3095                  |                 |                 |                 | 29 <b>66</b>     |

| PAM4 512b  | 3690                  |                 |                 |                 | 35               |

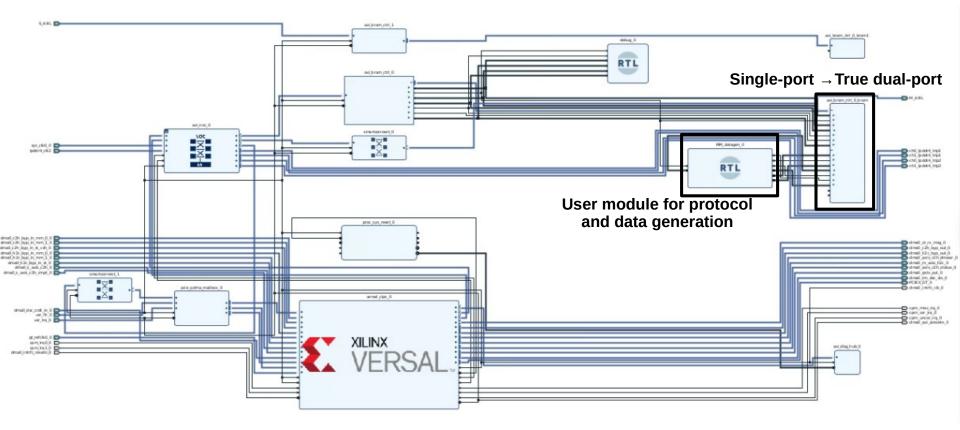

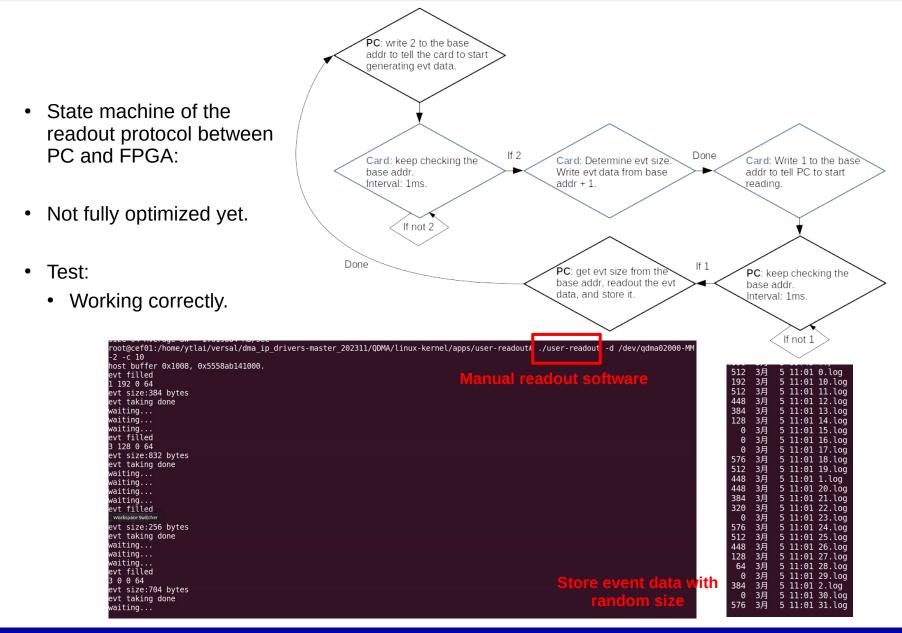

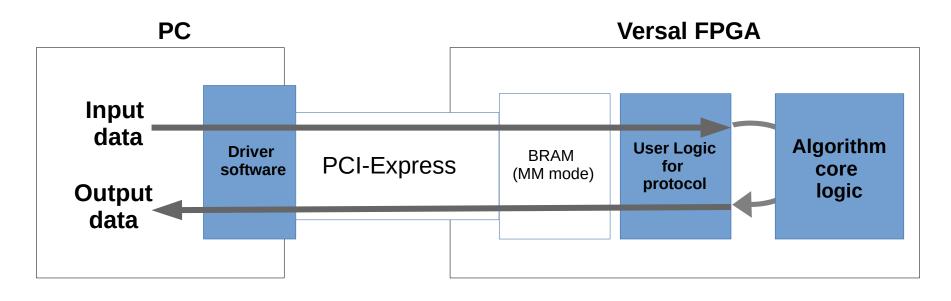

### **PCIe-CPM** test

- CPM-PCIe example from Xilinx: XTP712

- CPM: building block design for PCIe with integrating DMA, CIPS, NOC, etc.

- PCIe Gen4 x8: GTYP links are up. 16 Gbps per lane.

- Driver software: QDMA, also a Xilinx IP. ٠

- Data exchange test with the QDMA • software:

- We spent much time in mine-sweeping ٠

- Will start to make real protocol for event data readout purpose.

- Similar to the one in Belle II DAQ

| lardwa                                                                                                                        | are          |               | ? _ 🗆                      | L X DI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DRMC - DDRMC_1          | DDRMC -       | DDRMC_2 ×           |          |                     |                      |                                                            |                |                |     |

|-------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------|---------------------|----------|---------------------|----------------------|------------------------------------------------------------|----------------|----------------|-----|

| $\mathbf{Q} \mid \Xi \mid \Leftrightarrow \mid \boldsymbol{\beta} \mid \models \mid \gg \mid \equiv \mid \qquad \diamondsuit$ |              |               |                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Status Margins Analysis |               |                     |          |                     |                      |                                                            |                |                |     |

| Name Status                                                                                                                   |              |               |                            | Status   Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |               |                     |          |                     | ,                    |                                                            | L Chart (Fran  | - 01 - 0       |     |

| v Ng Quad_102 (4)                                                                                                             |              |               |                            | <b>^</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Status   Status         | Registers     |                     |          |                     |                      | Table   Chart (Freq 0) - Left Aligned   Chart (Freq 0) - C |                |                |     |

|                                                                                                                               | Pd CH_0      |               | 15.987 Gbps                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Name: DDRMC_2           |               |                     |          |                     | Q B                  | €   <b>\$</b>   P                                          | S Read Mode ✓  | Simple Pattern | ı v |

|                                                                                                                               | Pc] CH_1     |               | 15.977 Gbps                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |               |                     | Name     |                     | Left Margin (tap     | s) Center                                                  | Point          |                |     |

|                                                                                                                               | ₽d CH_2      |               | 15.97 Gbps                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |               |                     | ✓ Freq   | 0                   |                      |                                                            |                |                |     |

|                                                                                                                               | Pd CH_3      |               | 15.954 Gbps                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |               |                     |          |                     | ~ Bj                 | te 0                                                       |                |                |     |

|                                                                                                                               | ✓ № Quad_10: | 3(4)          |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Gate Tracking St        |               |                     |          |                     |                      | Nibble 0                                                   |                | 61             |     |

|                                                                                                                               | P⊲ CH_0      |               | 15.973 Gbps                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Message:                | No errors o   | detected during cal | ibrat    | ion.                | Nibble 1<br>V Byte 1 |                                                            |                | 61             |     |

|                                                                                                                               | Pig CH_1     |               | 15.963 Gbps                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Error:                  |               |                     |          |                     |                      |                                                            |                |                |     |

|                                                                                                                               | ₽d CH_2      |               | 15.98 Gbps                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |               |                     |          |                     |                      | Nibble 0                                                   |                | 62             |     |

|                                                                                                                               | № CH_3       |               | 15.984 Gbps                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |               |                     |          |                     |                      | Nibble 1                                                   |                | 62             |     |

|                                                                                                                               | 1 DDRMC_1 (L | PDDR4) (x0y0) | PASS                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Calibration             |               |                     |          |                     | ~ B                  | te 2                                                       |                |                |     |

|                                                                                                                               | DDRMC_2 (L   | PDDR4) (x1y0) | PASS                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Stage                   |               |                     |          | Status              |                      | Nibble 0                                                   |                | 62             |     |

|                                                                                                                               | DDRMC_3      |               | DISABLED                   | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Stage<br>SCAL STAGE.01  |               |                     |          | Status ^            |                      | Nibble 1                                                   |                | 62             |     |

| _                                                                                                                             |              |               |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |               |                     |          | S Pass              | ~ B                  | te 3                                                       |                |                |     |

| Properties 2 – C C X                                                                                                          |              |               |                            | CAL_STAGE.02_F0_MEM_INIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |               |                     | Nibble 0 |                     | 61                   |                                                            |                |                |     |

|                                                                                                                               |              |               |                            | CAL STAGE.04 F0 DQS GATE CAL SPASS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |               |                     | Nibble 1 |                     | 60                   |                                                            |                |                |     |

|                                                                                                                               |              |               | $\leftarrow$ $\rightarrow$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |               |                     |          | % Pass              | ~ B)                 | te 4                                                       |                |                |     |

| Select an object to see properties                                                                                            |              |               |                            | \CAL_STAGE.05_F0_WRITE_LEVELING             \CAL_STAGE.06_F0_READ_D0_CAL             \CAL_STAGE.07_F0_NRITE_D0_D0L_CAL             \CAL_STAGE.07_F0_NRITE_D0_D0L_CAL             \CAL_STAGE.07_F0_NRITE_D0_D0L_CAL             \CAL_STAGE.07_F0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_D0_NRITE_ |                         |               |                     |          | Nibble 0            |                      | 64                                                         |                |                |     |

|                                                                                                                               |              |               |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |               |                     |          | Nibble 1            |                      | 64                                                         |                |                |     |

| cl Con<br>Q   🗶                                                                                                               | · · · 9      | es Serial I   | /O Links ×                 | Serial I/O Se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RX PLL Status           | TX PLL Status | Loopback Mode       |          | Termination Voltage | RX Comr              | ion Mode                                                   | TXUSERCLK Freq | RXUSERCLK Fre  | q   |

|                                                                                                                               |              |               |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |               |                     |          |                     |                      |                                                            |                |                |     |

| · ~                                                                                                                           | 0            | Inject        | Reset                      | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ]                       |               | User Design         | ~        | 800mv ~             |                      |                                                            |                |                |     |

| n v                                                                                                                           | 0            | Inject        | Reset                      | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Locked                  | Locked        | User Design         | ~        | 800mv ~             |                      |                                                            | 499.512        |                | 292 |

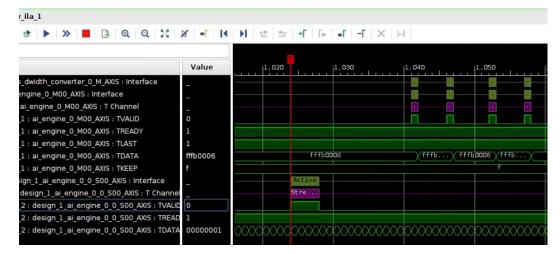

| 1 V                                                                                                                           | 0            | Inject        | Reset                      | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Locked                  | Locked        | User Design         | ~        | 800mv ~             | Program              |                                                            | 499.512        |                | 292 |