# CDCFE upgrade

Yu Nakazawa (KEK)

October 23, 2025

Belle II Trigger/DAQ Workshop 2025 @Umeda, Osaka

# Why we have to upgrade the CDC FEE?

Lack of Radiation tolerance of the optical module for CDCTRG

· Requirement: 1 kGy

· Tolerance: 0.3 kGy

This could be broken until the end of Belle II.

### Possible options

- · Swap to the same module mounted on the TRG board (CDC Merger), and use other optical module on it with minor? board modification

- Develop the new CDC FE satisfying the required radiation tolerance. This is the baseline plan while adding some new motivations.

### Motivations

Reduce ASIC crosstalk

Satisfy the requirement of the radiation tolerance (req. 1 kGy)

· H. Bae will report later

Transfer all hit data to CDCTRG

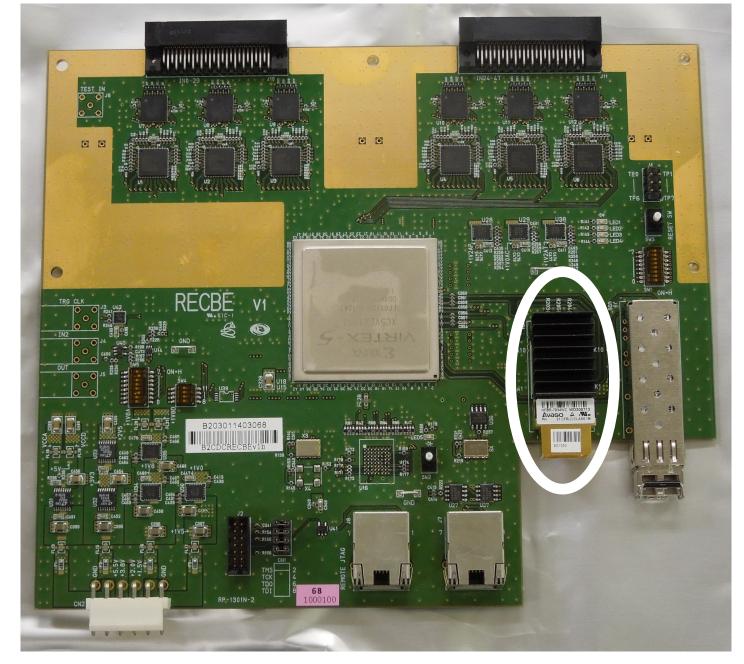

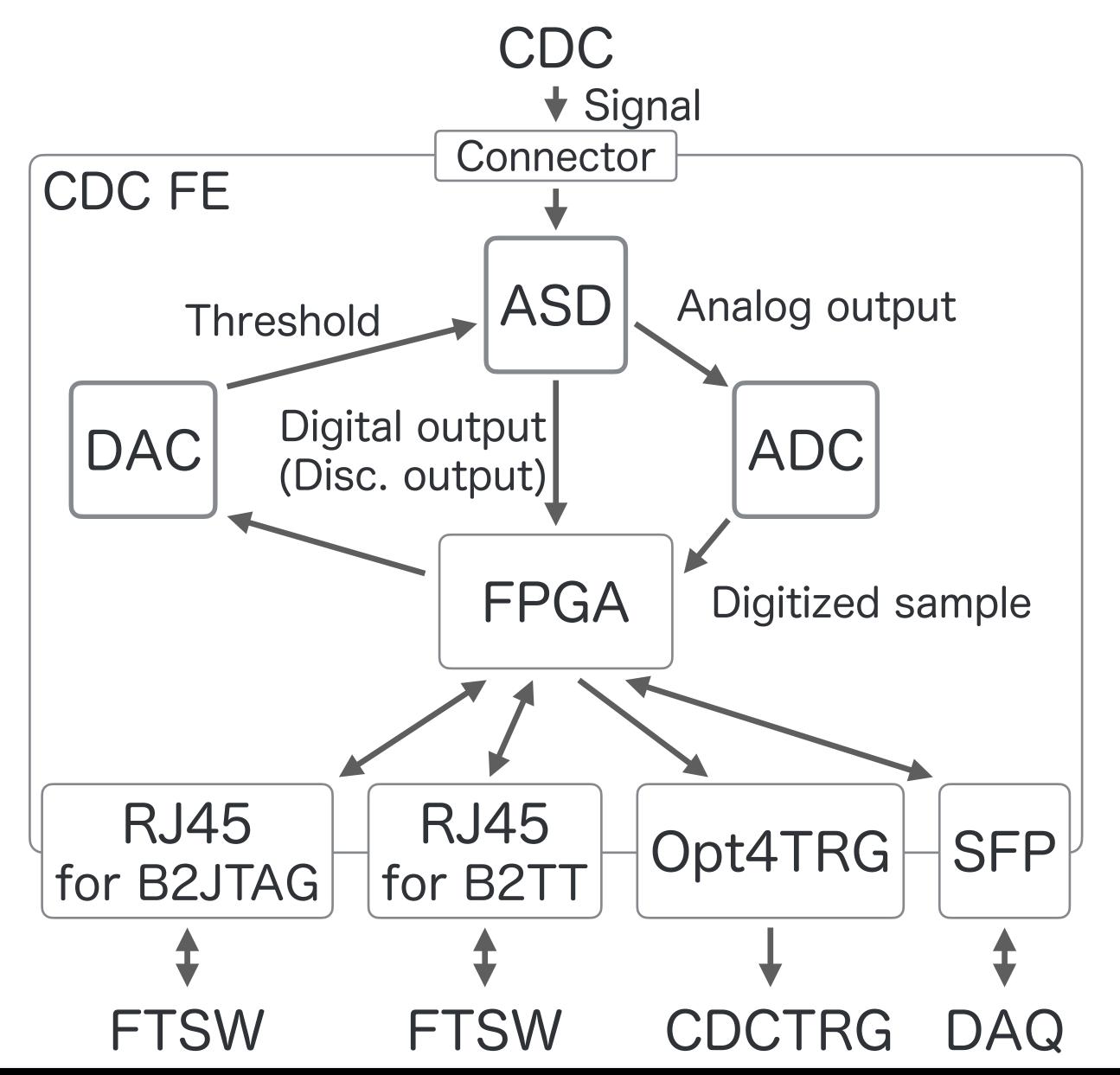

## Current FE

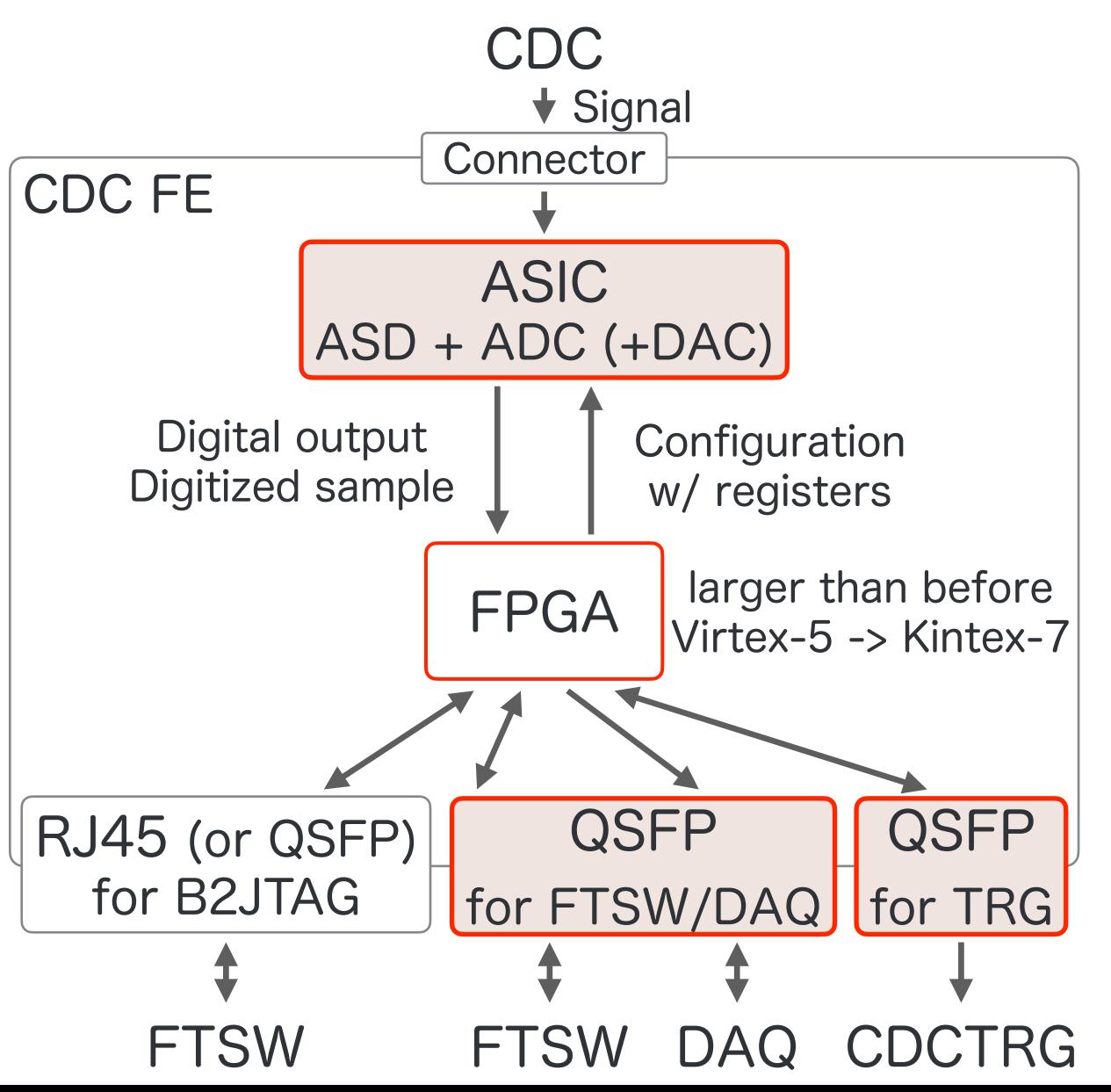

# Upgraded FE

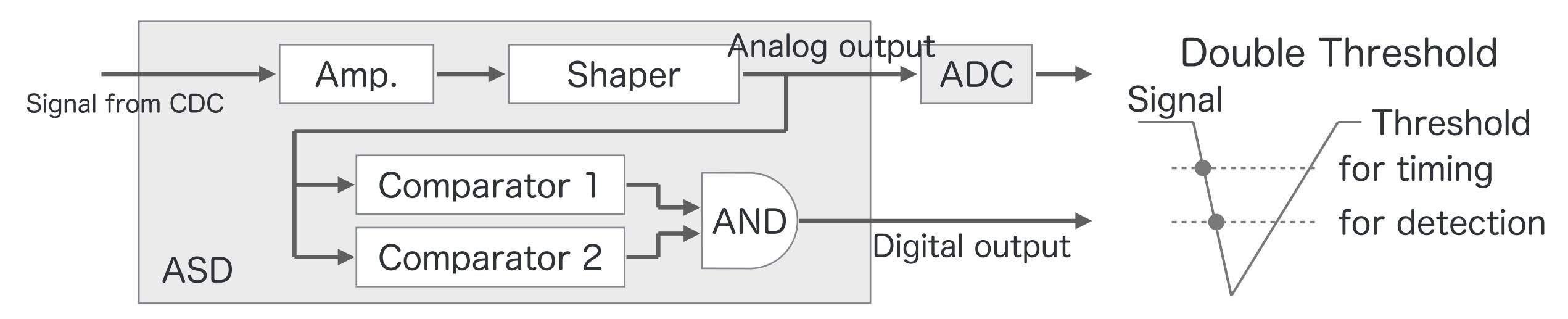

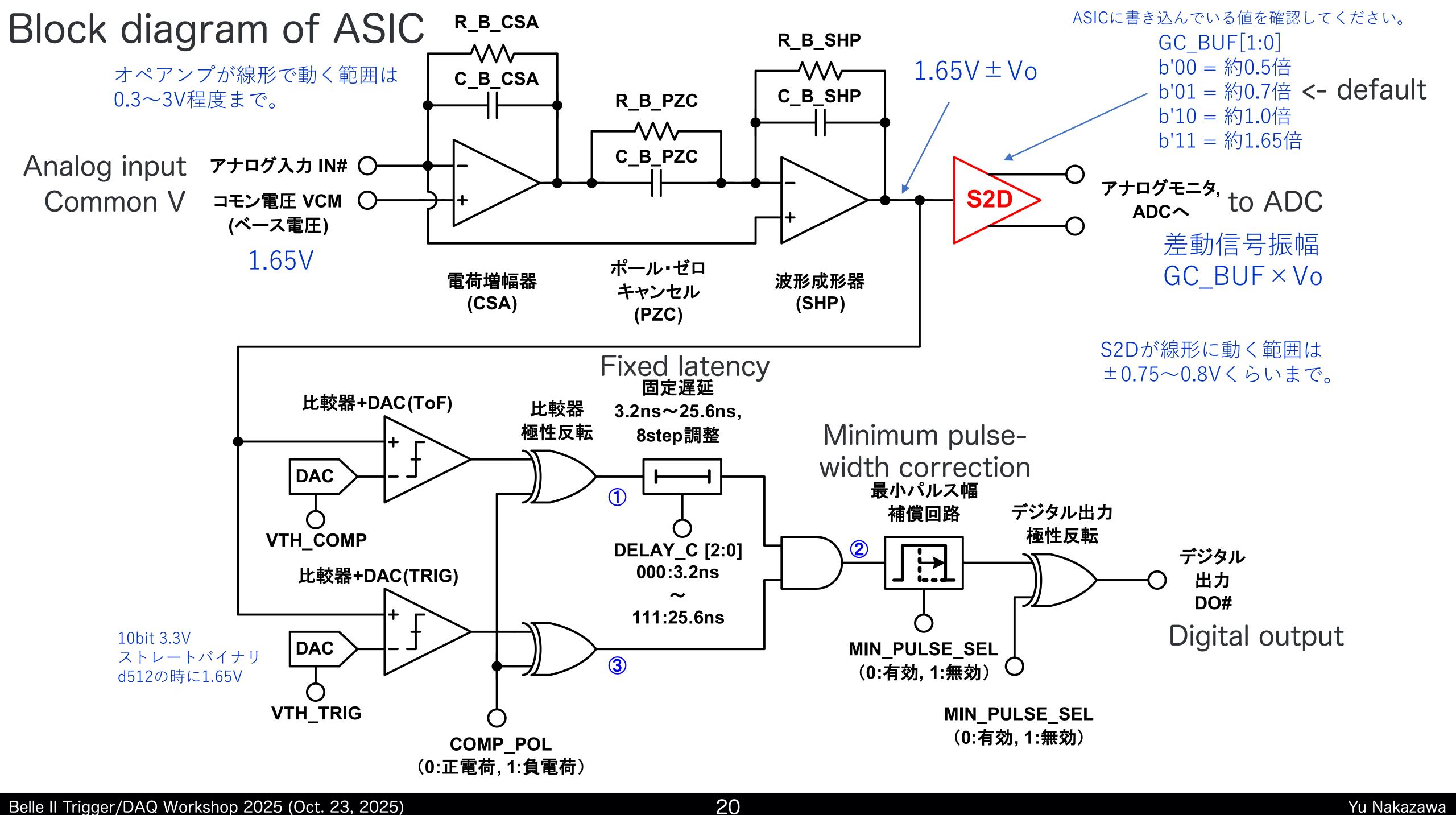

# ASIC design by M. Miyahara (KEK Esys)

### ASD+ADC in a chip (8 ch/chip)

- · Apply double thresholds for timing information

- Can adjust parameters by accessing registers

- · R/C for amp. and shaper, timing, and so on

- · Suppress crosstalk by differential-type circuit

|                          | Current                      | New            |  |  |  |

|--------------------------|------------------------------|----------------|--|--|--|

| Gain [V/pC]              | (Analog) 1.1,<br>(Digital) 7 | 0.9            |  |  |  |

| Linearity of gain [pC]   | 0.4                          | 1.1            |  |  |  |

| ADC sampling [MSPS]      | 31.25                        | 63.5           |  |  |  |

| ADC                      | 10 bit, 2 Vp-p               | 10 bit, 2 Vp-p |  |  |  |

| Compactor                | X                            | 10 bit, 3 Vp-p |  |  |  |

| Analog crosstalk [mV/pC] | 14                           | 1.0            |  |  |  |

| Power (ASD+ADC) [mW/ch]  | 134                          | 41.3           |  |  |  |

|                          |                              |                |  |  |  |

Note: ADC sampling can be up to 100 MSPS for new ASIC

## Motivation 1: Crosstalk reduction

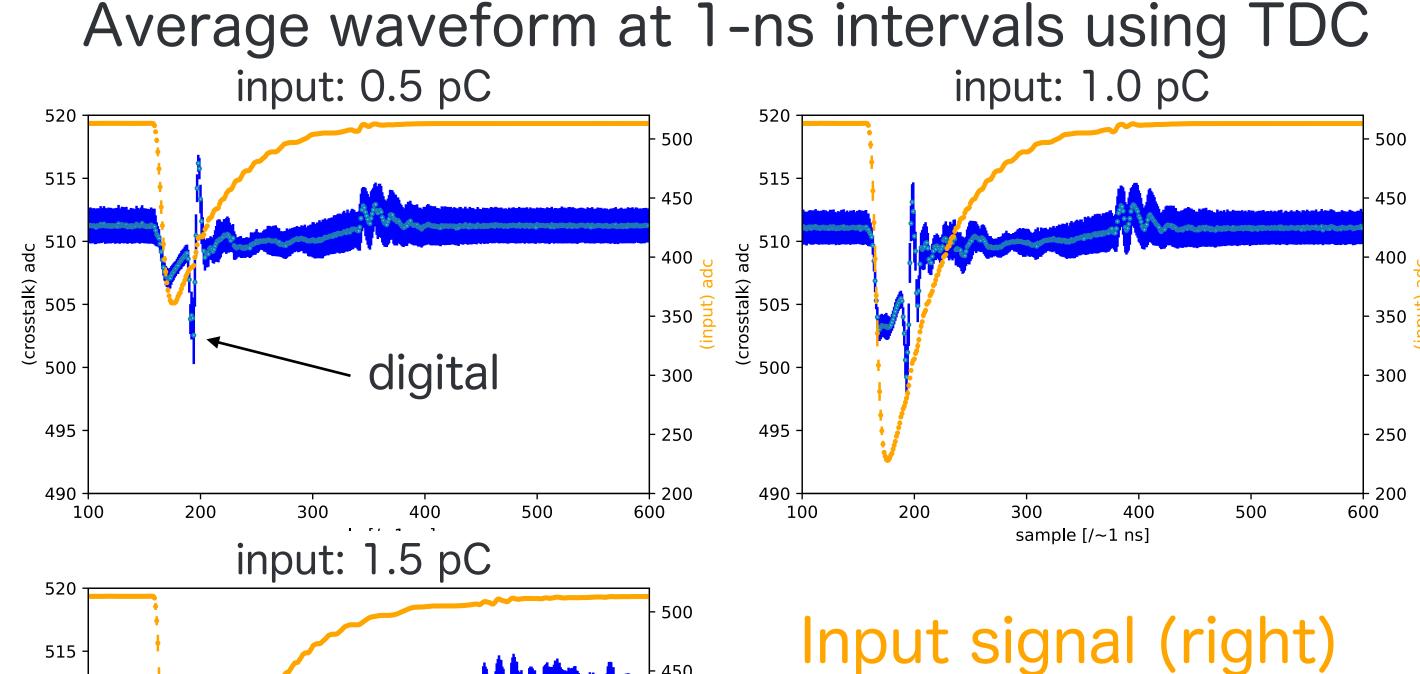

#### What is crosstalk? 1pF capacitor Input Voltage→Charge Waveform · Signal from waveform: 10 V -> 10 pC Generator Input signal (ch4) · ASIC Threshold (baseline = 511) Trigger 508 for both CDC FE Overlaid waveforms (ADC value vs sample) PC ch0 ch3 Input board ch4 This is Crosstalk Prototype

# Motivation 1: Crosstalk reduction Xiaodong Shi, Yu Nakazawa

Two types of crosstalk were found.

### Analog-part-induced

- · correlated with the input charge

- · occurs simultaneously with the input

### Digital-part-induced

- Independent of the input charge (<10 ADC)

- occurs with a delay after the input

- + small baseline fluctuation

The double-threshold technique can still cut most crosstalk. Further studies for digital-induced crosstalk are necessary.

250

fluctuation

500

analog

### Crosstalk (left)

(2024.10.03)

input channel: 1-7

(simultaneous inputs)

target channel: 0

200

(crosstalk) adc 200 200 200

495

## Motivation 2: Radiation tolerance

### Original radiation requirement for 10-year operation

- · Neutron: 1x10<sup>12</sup> n<sub>1-MeV</sub>/cm<sup>2</sup>

- · Gamma ray: 1 kGy

- · I don't know how these numbers were determined. I'd like to re-evaluate them considering recent conditions.

### <u>Strategy</u>

- · Use parts identical to those already evaluated in the current modules as possible as we can. (e.g., regulators)

- · Evaluate and select any new components individually. (done)

- · Optical module: QSFP+ 40G

- · Power section: LVDS buffer, Operational amplifier, Voltage monitor, etc

- · Clock: Clock Jitter Cleaner

- ASIC (-> having sufficient tolerance)

- · Perform irradiation tests on a FE prototype before mass production (not yet)

# Motivation 3: High-rate TRG data transfer

#### Upgrade point: 14.8 Gbps -> 40 Gbps

- · Assuming an 8b/10b protocol, the payload is 80% -> effective rate is 32 Gbps

- · The impact on the TRG performance is under discussion in TRG.

- · In the early phase of operation, we can run with the current data format and algorithms of CDCTRG.

#### Raw data size on the CDC FEE FPGA

- · 1 sample per channel: ADC 10 bits + TDC 16 bits

- · ADC sampling: 63.5 MHz

- The ADC sampling period is split into 16 sub-intervals to carry TDC timing. LSB = 1ns

#### Possible data sent to TRG

- · ADC: 9 bits/ch/sample (baseline is 511, and chamber signals are lower than it.)

- · TDC: 4 bits/ch/sample

- · Within one sample, only the fastest TDC value per channel is valid.

- · Multiple TDC hits in the same sample are not recorded.

# Possible data format (Req.: < 32 Gbps)

#### Scenario 1: Full data -> 39.624 Gbps X

- · 1 sample per channel: ADC 9 bits + TDC 4 bits

- · Transfer sampling rate: 63.5 MHz

- · If CDCTRG also handles CDC DAQ, additional 10 Gbps for the current DAQ is possible.

- · This needs one extra QSFP lane (1/4 QSFP) in addition to one QSFP -> Firmware/cabling need to be changed.

#### Scenario 2: Half sampling rate -> 21.336 Gbps O

- · 1 sample per channel: ADC 9 bits + TDC 5 bits

- Transfer sampling rate: 31.75 MHz

- · Sum/Average for down-sampling is necessary.

- · (Full ADC = 10 bits is still possible. -> 22.86 Gbps)

#### Scenario 3: Half ADC resolution with full sampling rate -> 30.48 Gbps O

- · 1 sample per channel: ADC 5 bits + TDC 4 bits

- · Transfer sampling rate: 63.5 MHz

# Performance

# Performance study

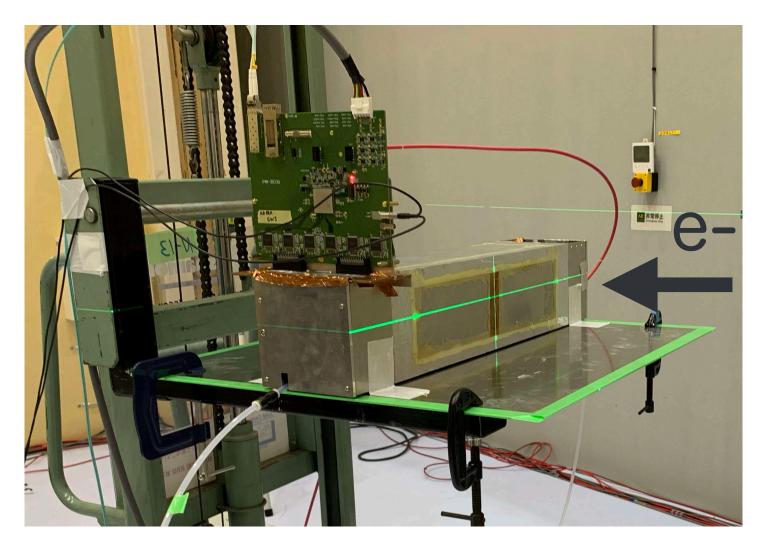

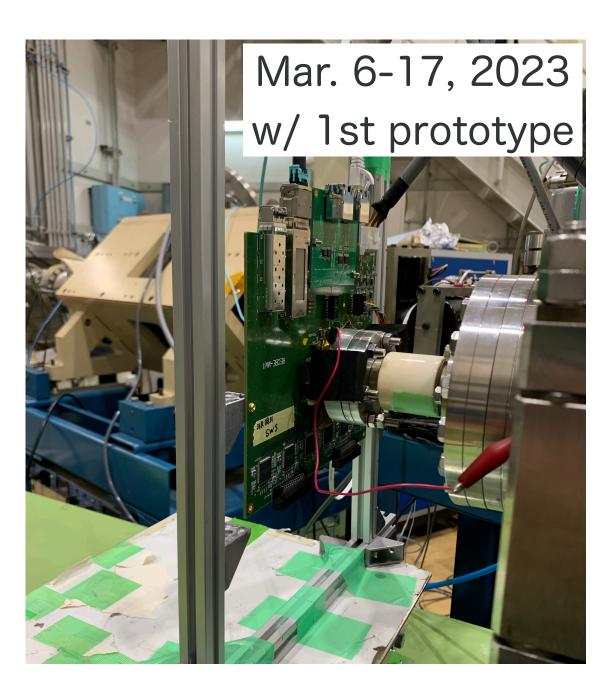

· Tested at the KEK PF-AR test beamline

· Beam: 3-4 GeV electrons, DAQ rate ~100 Hz

· Trigger: coincidence of 2 scintillators in the beamline

· Main target: spatial resolution

Measurements under identical conditions for both the new and current modules.

(Same HV, signal thresholds (as close as possible), and analysis tools)

[Chamber]

Cell: 15 mm x 15 mm

Layout: 8 layers

44 wires

Gas: He:C<sub>2</sub>H<sub>6</sub>=50:50

HV: 2.3 kV

w/ (NPC) Y.Ma, M.Niiyama, M.Takizawa (UT) A.Gonnokami, (OMU) M.Oki, E.Nakano

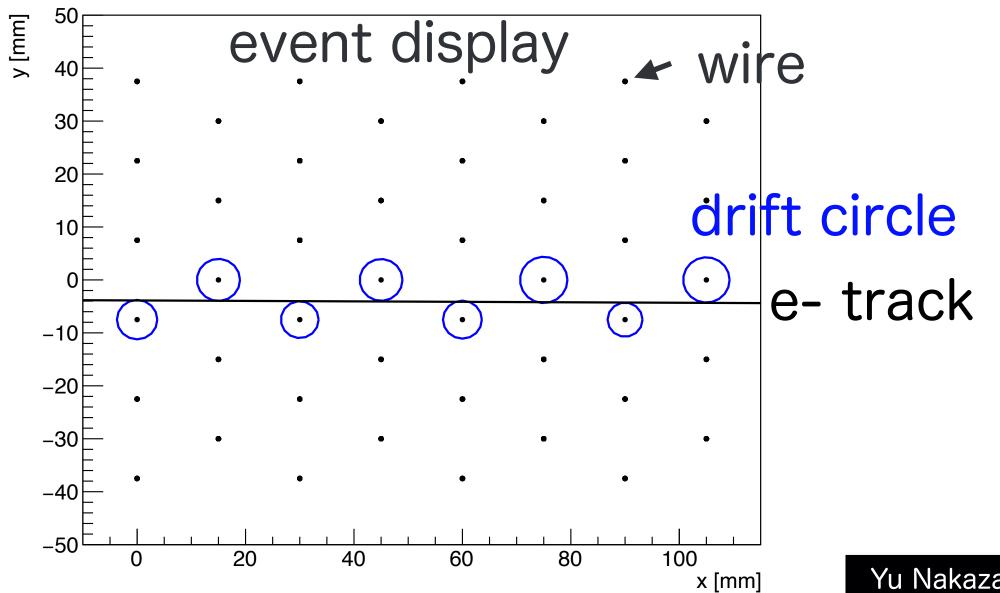

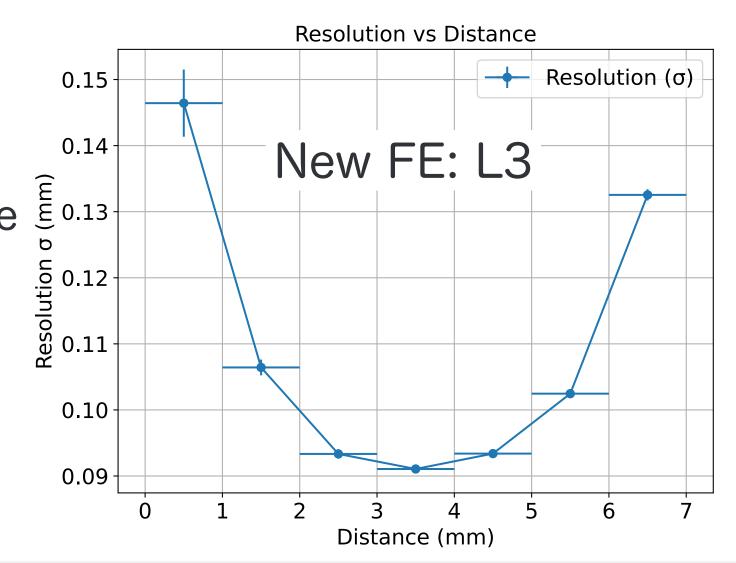

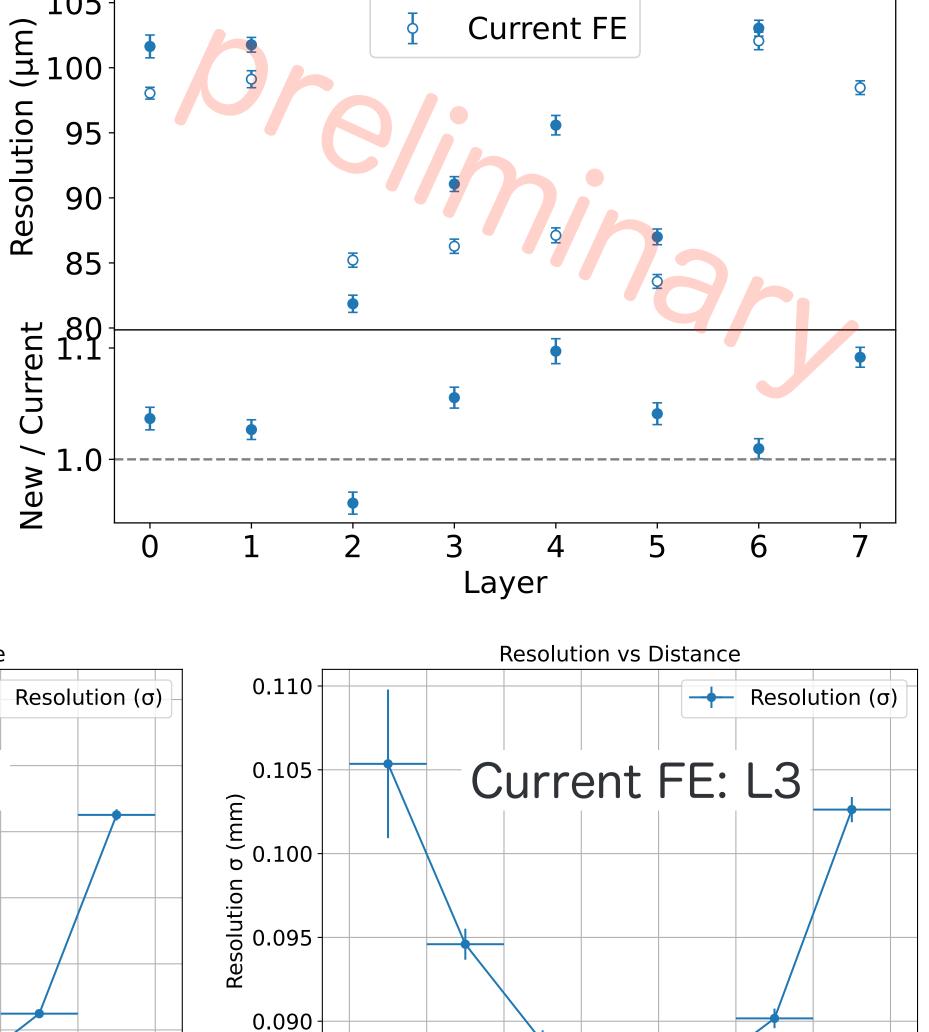

# Spatial resolution

The spacial resolution is ~1.05 times higher than that of the current module.

- · Looking at drift distance 3–4 mm to check the best resolution.

- Many charged particles have p < 1 GeV/c in physic runs; multiple scattering dominates.

- The impact on the analysis may be minimal?

- -> needs to be confirmed

Issue: 30-40% worse resolution near the wire and at the cell edge

- Possible reason1: Because the used chamber has a staggered-cell geometry, track reconstruction near the wires and at the cell edges is difficult. A ~5% difference \$\frac{1}{6} 0.13\$ in resolution may be amplified

- Possible reason2: With the lower ASIC gain, the time-walk effect for small signals may be significant.

0.085

New FE

Current FE

Distance (mm)

# Summary

The current CDC FE may need to be replaced in the future due to insufficient radiation tolerance of the optical module.

#### Upgraded FE module is almost finalized.

- · New dedicated ASICs have already been developed.

- · Parts meeting the requirement of the radiation tolerance have been found.

#### Performance evaluation is in progress.

- · Basic performance of ASIC has been measured.

- · Spatial resolution and dE/dx resolution have been evaluated using a test chamber.

Next: better understand the spatial resolution and evaluate performance at lower gas gain

· Plan: perform a beam test with the test chamber

We would like to start mass production in 2026 if the remaining issues are solved.

· Review will start soon (1st: next week).

### List of main tasks

#### Radiation hardness

- · Perform irradiation tests using a FE prototype before mass production.

- · Re-consider the requirements of the radiation tolerance including recent machine conditions.

#### **CDCTRG**

· Consider what we can do with such data.

#### <u>Perfomance</u>

- · Perform a detailed study of digital-part-induced crosstalk.

- · Evaluate the impact on the momentum resolution, and determine acceptable limits for degradation of the spatial resolution (performance study)

- · Investigate why the resolution degrades at the cell edges.

- · Evaluate the spatial resolution at lower gas gain as discussed recently.

# beam test

#### **Others**

· After fixing the firmware, the power consumption needs to be measured.

Backup

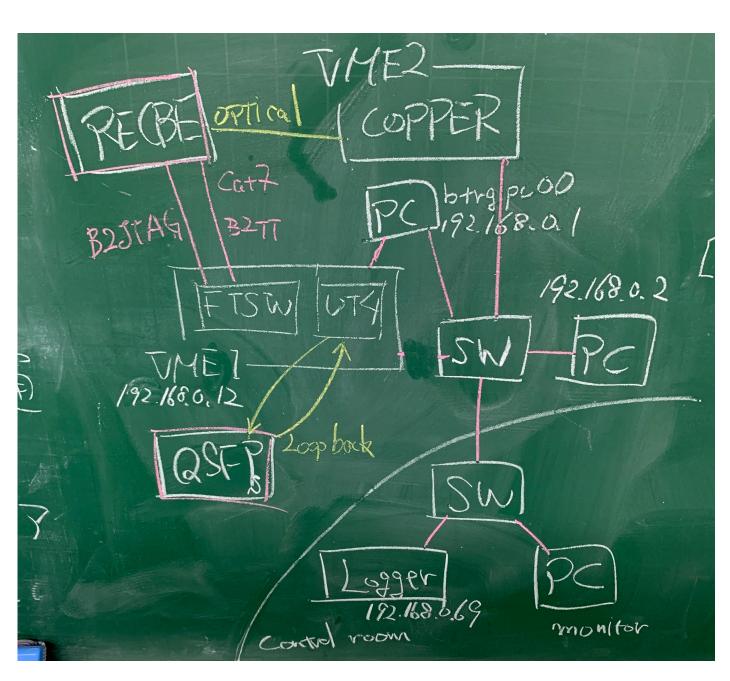

### Current FE

REPETOPTICAL COPPER

POSTAGE BETT PC 192/68.0.2

FISH UTSI UTSI 192/68.0.2

POSTAGE SW PC

192/68.0.12

PC 192/68.0.69

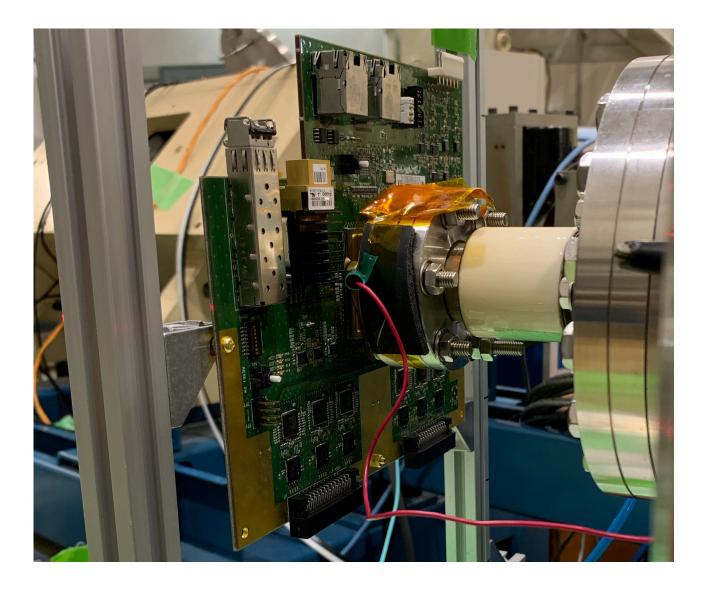

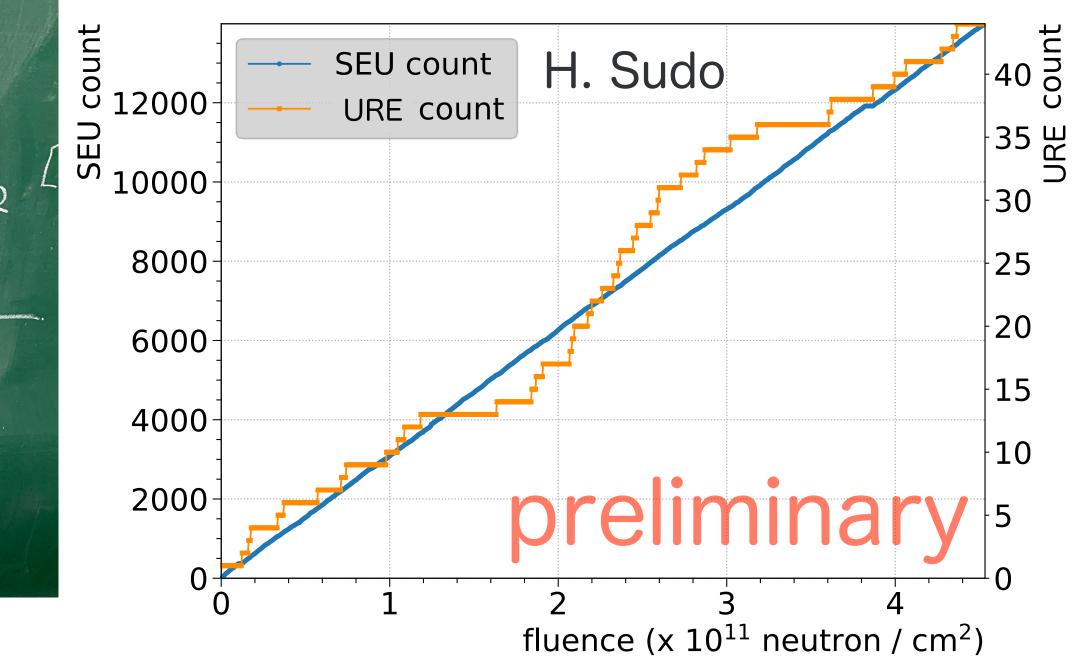

w/ T. Koga, H. Sudo, T. Hotta, M. Niiyama, M. Sumihama

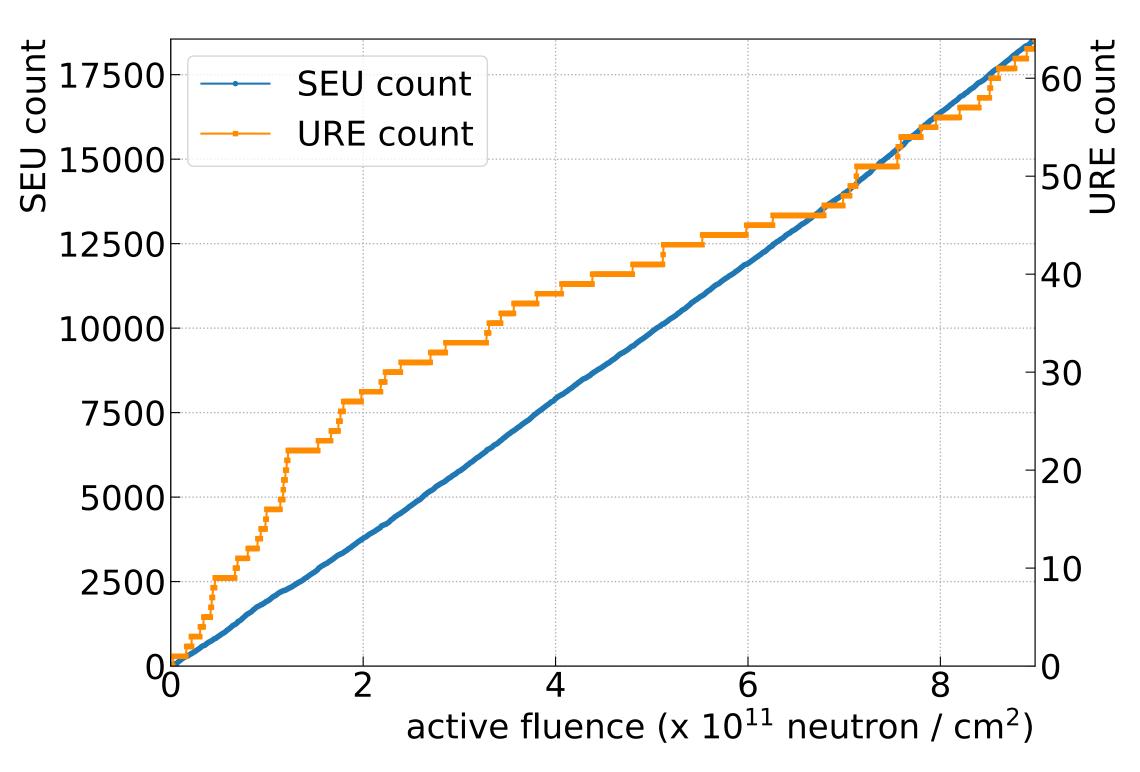

Total fluence: 4.5 x 10<sup>11</sup> n/cm<sup>2</sup>

SEU Controller successfully detects and corrects SEUs

- · SEU rate: 3.1 x 10<sup>-8</sup> SEU/(neutron/cm<sup>2</sup>)

- · URE rate 1.0 x 10<sup>-10</sup> URE/(neutron/cm<sup>2</sup>)

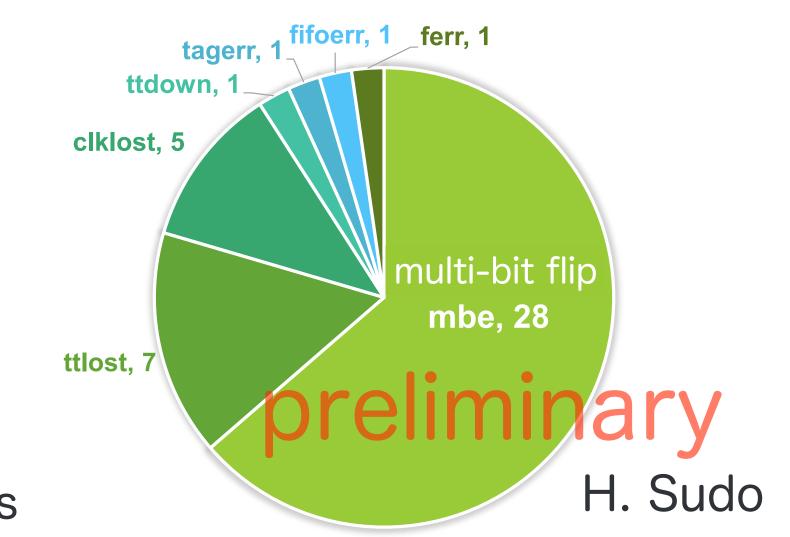

- · URE = UnRecoverable Error including multi-bit flips and all the FTSW-detected errors

- · requires FPGA re-configuration to fix

The error check cycle on b2tt is fast, so it detects SEUs to be corrected before the repair module does. => major errors in the past physics runs

### Neutron irradiation for FPGA

w/ T. Koga, H. Sudo, Y.-T. Lai, T. Hotta, M. Niiyama, M. Sumihama

Neutron beam: 9Be + d (3 MeV) -> 10B + n (~2 MeV)

Test firmware: almost the same as the current CDC FEE

· No change in th FPGA between the 1st and 2nd prototypes.

Result: No permanent damage has been observed.

- · SEU rate: 2.1 x 10<sup>-8</sup> SEU/(neutron/cm<sup>2</sup>)

- · URE rate 7.1 x 10-11 URE/(neutron/cm<sup>2</sup>)

(\*) UnRecoverable Error (URE) requires firmware configuration to fix this error

### Neutron irradiation for FPGA

w/ T. Koga, H. Sudo, Y.-T. Lai, T. Hotta, M. Niiyama, M. Sumihama

### Error related to trigger communication

- · A PRBS pattern is transmitted.

- · Detections of errors in the pattern: 14 times

### Current vs Upgraded FEE

pseudorandom binary sequence: PRBS

- · double logic size, but the error rate is equivalent or possibly smaller than xc5vlx155t!!

- thanks to the smaller technology of FPGA.

|                           | Config. logic block # of slices | technology<br>[nm] | SEU rate<br>[n/cm²]    | URE rate [n/cm²]        |              |

|---------------------------|---------------------------------|--------------------|------------------------|-------------------------|--------------|

| Current FEE<br>xc5vlx155t | 24,320                          | 65                 | 3.1 x 10 <sup>-8</sup> | 1.0 x 10 <sup>-10</sup> | <b>^</b> 0/2 |

| Upgraded FEE xc7k325t     | 50,950                          | 28                 | 2.1 x 10 <sup>-8</sup> | 7.1 x 10 <sup>-11</sup> | J 70         |

Note: Since conditions are different, the URE rate may not be the same as during physics runs.

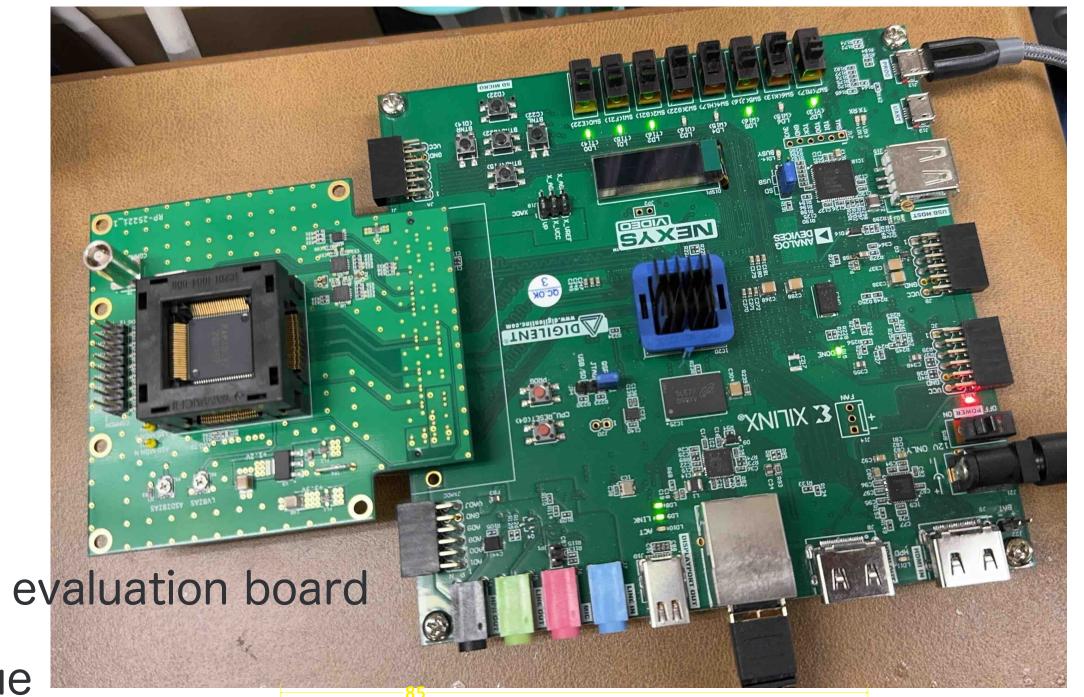

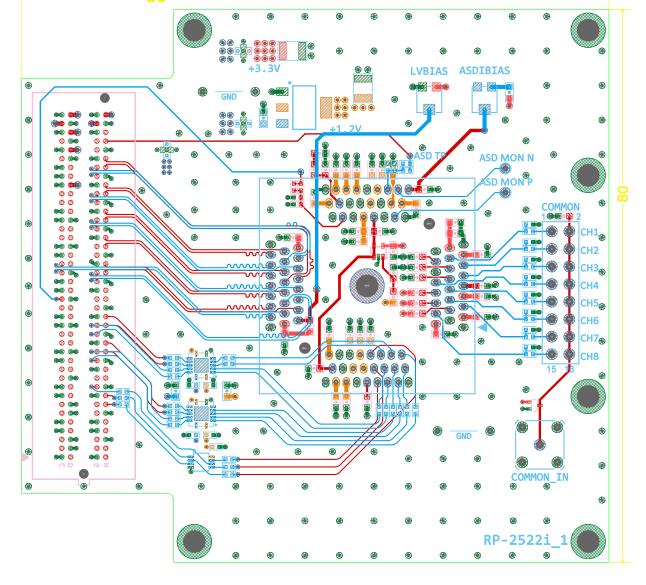

### ASIC evaluation board

### Current status

- · Evaluation board has already been developed.

- · ASIC configuration succeeded.

- · [Issue] ADC readout is not stable.

- · The ADC output looks correct using an oscilloscope.

- · According to the developer of ASIC, it may be an ASIC issue rather than the evaluation board

- · It (PLLCTRL) may be sensitive to noise / ground fluctuation.

- · This could be a socket-mount issue on the board.

- No problem about the ASIC soldered on the prototype module

### Next step

- · Reconsider whether this issue can be fixed.

- · If not, we have to consider how to check the ASICs before mounting on modules.

# Performance test w/ test chamber

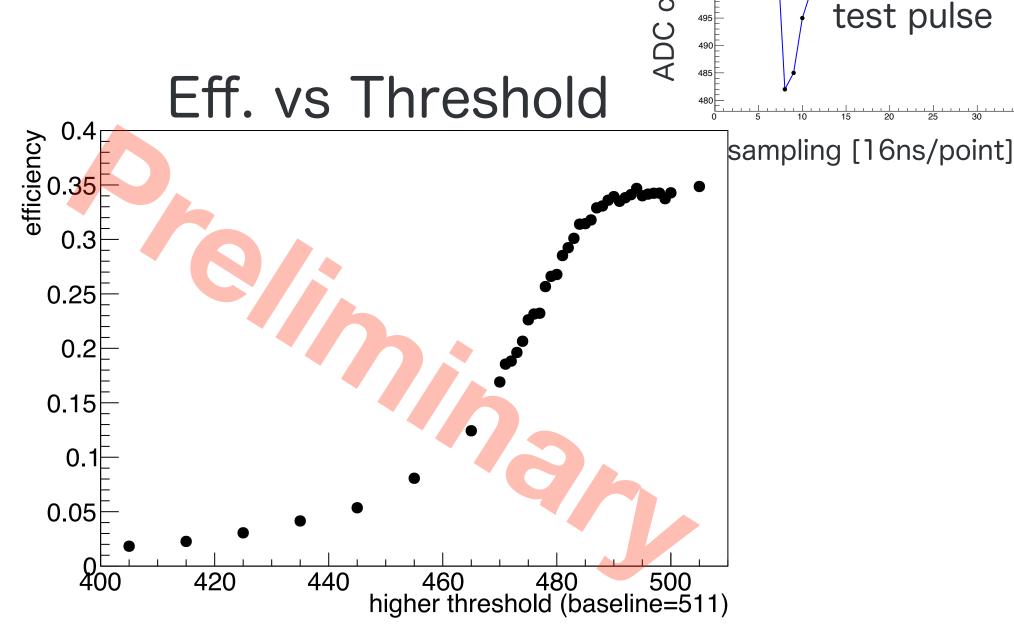

### [Threshold scan]

- · The threshold for detection (not timing) was changed.

- eff. = [# of events w/ TDC] / [# of triggers]

- · The detection efficiency also changes as the threshold value changes.

- ⇒ Threshold works as expected.

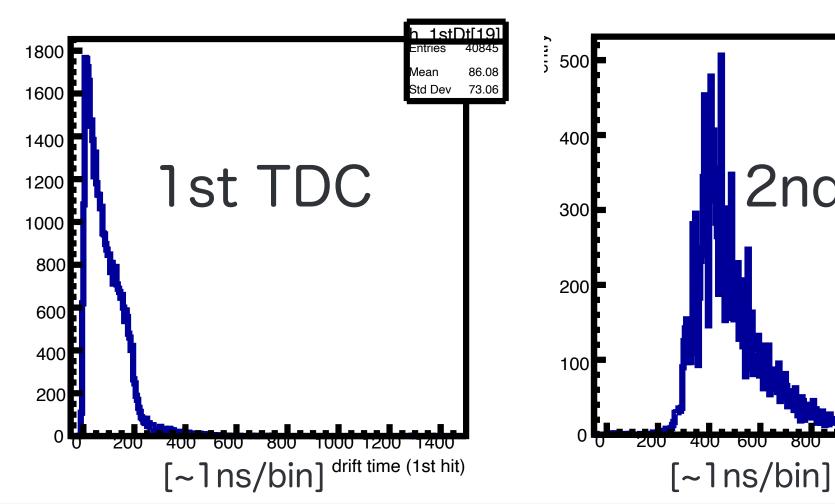

### [Check of general parameters used in analysis]

- · No noise ADC peak thanks to the double-threshold scheme

- · Reasonable 1st-TDC distribution

- Many 2nd-TDC hits ⇒ under investigation..

# Performance test w/ test chamber

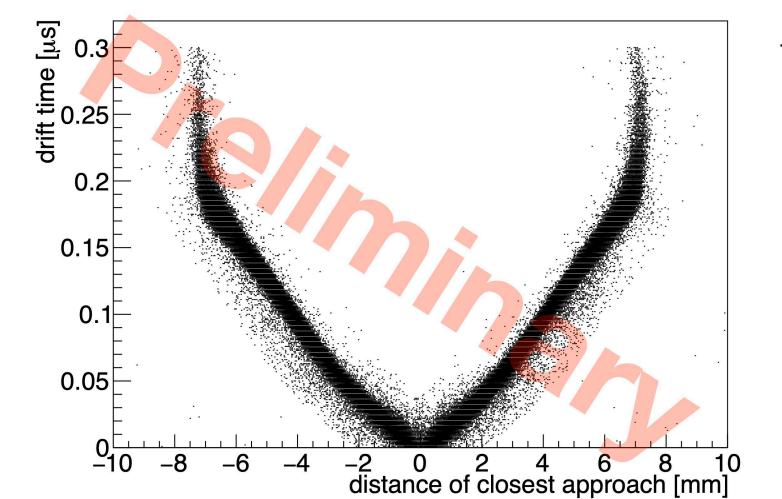

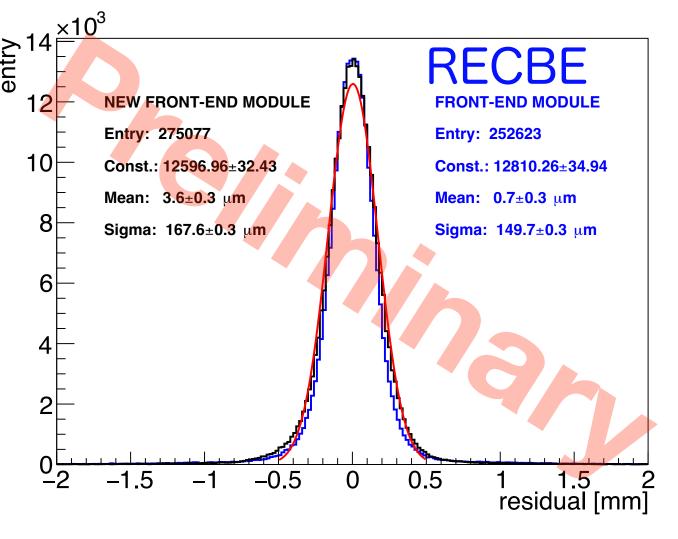

The same tracking code can be applied to RECBE and RECBE Mk-II data. These results are obtained after the

5th iteration of the tracking process.

#### [Spatial resolution]

- · Normal shape of the XT relation

- · Worse spatial resolution than RECBE's

- · RECBE Mk-II: 167.6 μm, RECBE: 149.7 μm

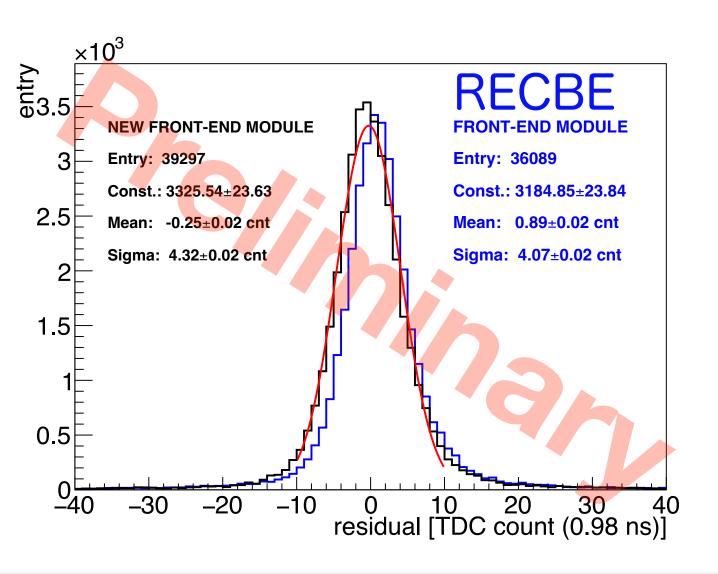

#### [Timing resolution]

- · Residual = (TDC<sub>Layer0</sub> + TDC<sub>Layer4</sub>)/2 TDC<sub>Layer2</sub>

- · Negatively shifted mean value

- · A little worse timing resolution than RECBE's

- · RECBE Mk-II: 4.32 cnt, RECBE: 4.07 cnt

- Thresholds are not the same! due to the smaller amplitude for the comparators in ASIC

- · I need comments from the tracking group on how much it will affect the physics.

- · Parameter tuning for the ASIC amplifiers will be tried.

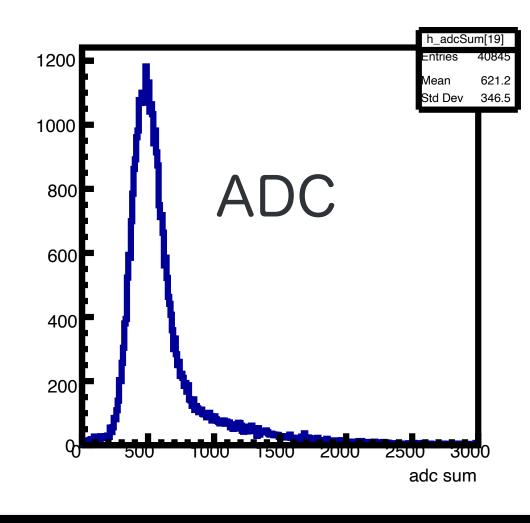

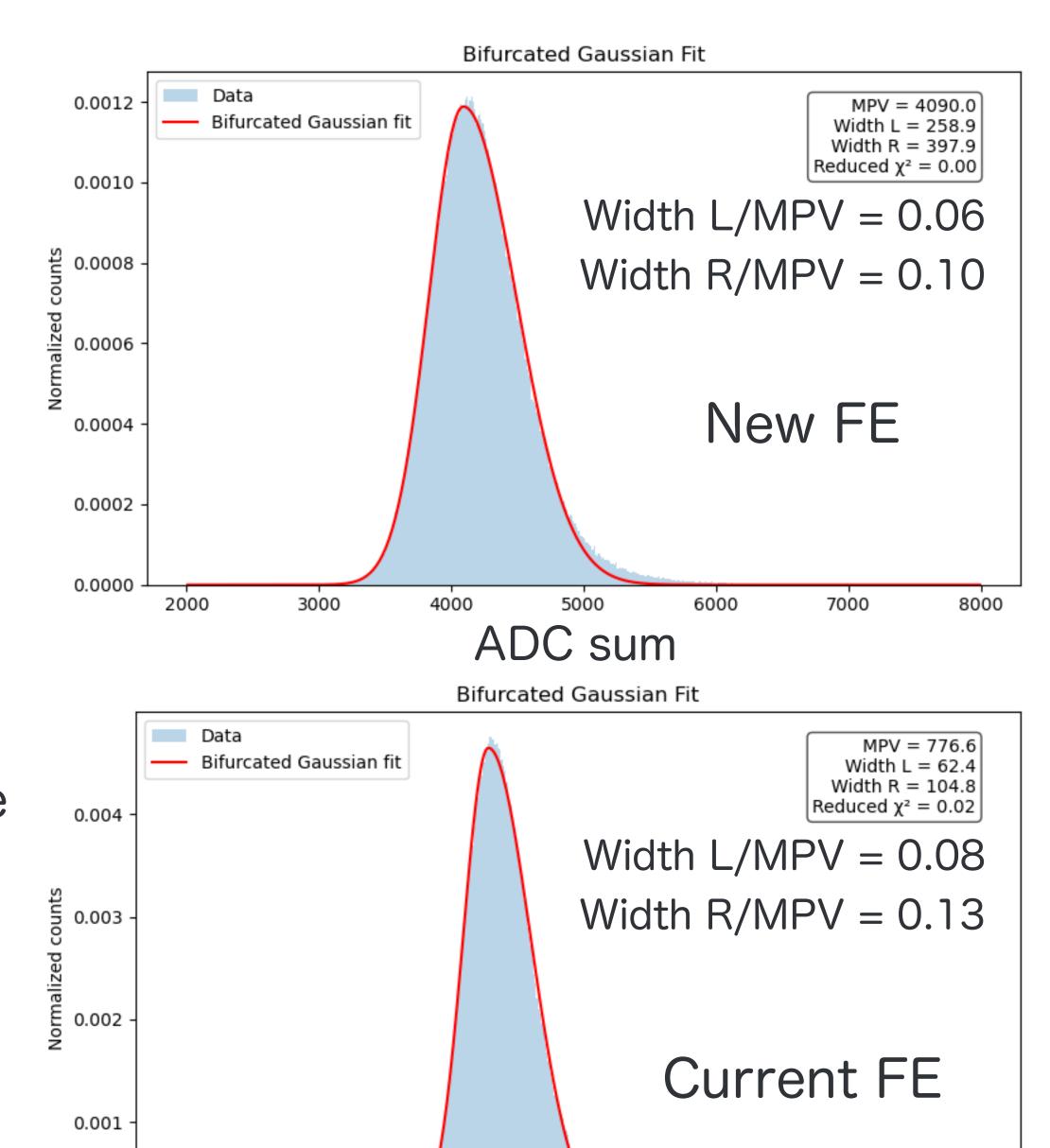

# dE/dx resolution

### Analysis workflow

- · Select events with exactly one hit in each layer

- · Compute the ADC sum over a 1-us window

- · Since RECBE records 1 us of data, it sets any samples below the baseline to zero (ignoring undershoot)

- Discard the highest and lowest ADC sums, then sum the remaining ADCs for six layers.

- · Normalize the distribution width to its peak amplitude and compare with the current module.

- · Fit the spectrum using a bifurcated Gaussian

### Result: new FE exhibits a 30% narrower width

The reason is still unknown..

(Larger linearity region of ASIC??)

1000

ADC sum

750

1250

0.000

250

500

2000

1750

1500

## Remaining concerns

#### Worse spatial resolution than the current FE

· As discussed before

#### Performance at lower gas gain

- · Since the ASIC was designed before the recent discussions on CDC performance, its gain is not taken into account.

- · ASIC gain is smaller than the current ASD, so performance degradation is a concern.

- · According to the developer, tuning R/C values in the amplifier/shaper may increase the gain by 5-10 times.

#### Study: evaluate spatial resolution in a tracking study using a test chamber

- · [Pre-study] scan R/C and find the optimal settings.

- · Check if spatial resolution improves.

- · Run with lower HV to reduce gas gain, and then evaluate the performance (not only spatial resolution)

- · Schedule: middle or late November if I have time to prepare.

### Status of readiness

#### Circuit desing

- · Only minor modifications remain.

- · All known changes are listed.

#### Parts procurement

- · All fixed chips have been purchased.

- · Parts that might be unnecessary depending on the final FE design have not been ordered.

- · ASICs: we need to test.

- · We are still working through issues with the evaluation board.

- · We use a replaceable socket for replacing chips, but with this socket the ADC readout is not stable.

#### **FPGA Firmware development**

- · Signal-processing logic equivalent to the current firmware has been developed.

- · We already tested the firmware running with the current DAQ and TRG (in PocketDAQ). Once it is integrated, the firmware development will be completed.

- · For deployment, we will need to prepare new scripts to configure the ASIC.

- · [Task] After fixing the firmware, the power consumption needs to be measured.