# Chip layout & Mechanics/Cooling/Integration

(ALICE: learnt that lesson)

S. Bettarini - INFN & Univ. Pisa

On behalf of the VTX Mechanical «Team»

## Belle II Vertex Detector Upgrade Spec's

Transparent and precise silicon pixel detector for vertexing in ultra high luminosity:

$$\mathcal{L} = 10^{36} \text{ cm}^{-2}\text{s}^{-1}$$

, TID = 100 Mrad,  $\phi = 10^{14} \text{ n-eq}$

#### Target:

- Fully monolithic vertex detector

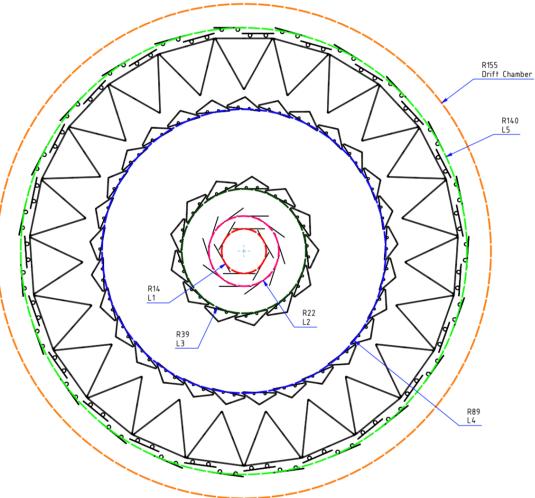

- Radius range [14,140] mm

- 30x30 μm² pixel pitch (single point res. 10-15 μm)

- T ~ 25-100 ns integration time

- Total power budget ~ O(kW)

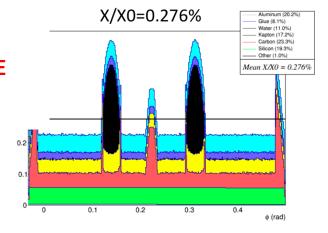

- $0.1\% X_0 \text{ (inner)} 0.3 \rightarrow 0.5\% X_0 \text{ (outer)}$

The choices on the (1!) chip design have a high IMPACT on the module/ladder mechanics!

After setting the general VTX spec's, their actual implementation in a conceptual detector design depends strongly on the «candidate chip» layout.

VTX mechanics provides some geometrical requirements on the chip dimensions.

To make a (common) step forward in the design of the module/ladder prototypes, it is needed to make hypotesis on the layout of the candidate chip, according to the constraints dictated by the chosen (TJ 180 nm) CMOS process/technology.

2

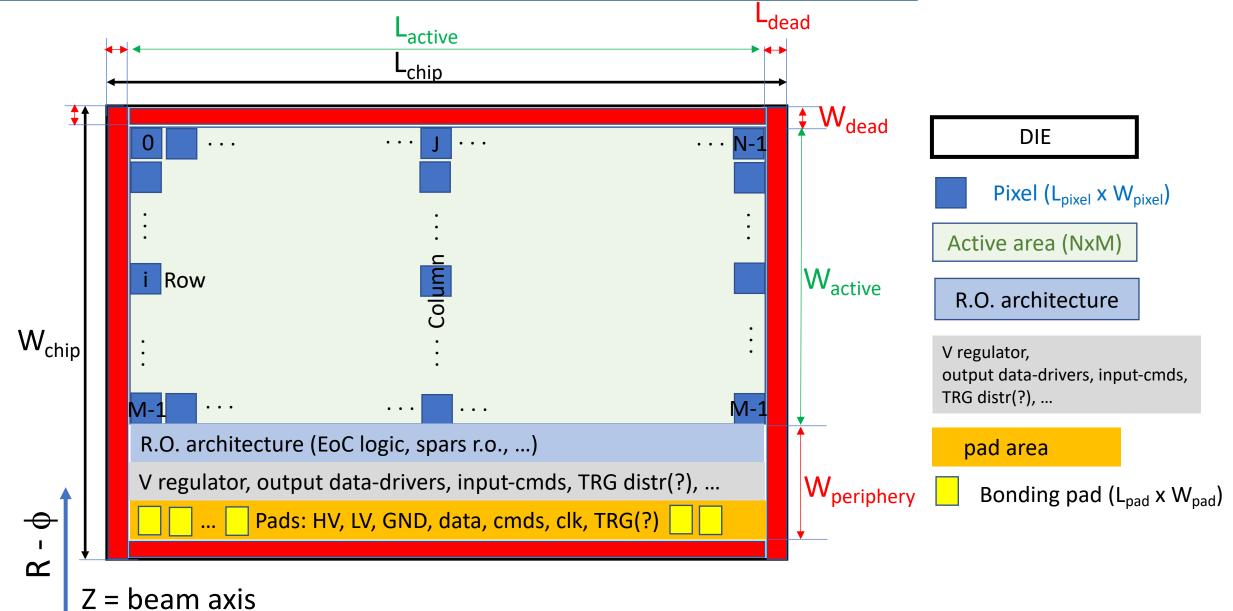

## MY (NAÏVE) IDEA ON the "FINAL CHIP" LAYOUT

## Questions (to the designers of "OBELIX"):

- Consideration on efficiency/cost → 1! Chip for the whole VTX, right?

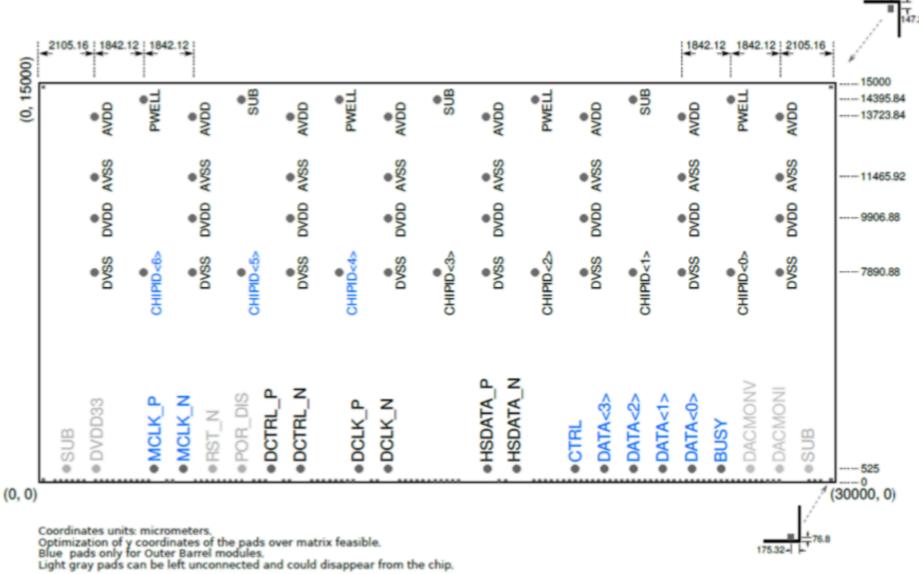

- Can be all the pads placed only on one side (on the periphery) of the chip, to have dead-region only on one  $(r-\phi)$  side of the module/ladder? Or power pads to the matrix and to the periphery must be routed/taken separated?

- e.g.: ALPIDE has power/bias pads all over its surface (perhaps to distribute power w/o significant drop). This would always need a flex-circuit on the module, with deep-access bondings, also for the VTX inner layers!

- thickness

50µm (IL)

100µm (OL)

Chip chip

Chips alignment

FPC wire bonding

FPC

Araldite 2010 50µm (B)

100µm (OB)

Araldite 2010 50µm (B)

100µm (OB)

Silicon

FPC

- Identified design: CMOS -process TJ-180 nm:

- are there limits on the max.  $L_{chip} / W_{chip}$ ?

- stitching? (the larger the chip, the better for the oVTX ladder).

- edge-less: do we have idea of L<sub>dead</sub> / W<sub>dead</sub>? Guard ring(s)?

- After implementing all the wanted "feature"

- estimated P<sub>specific</sub> < 200 mW/cm<sup>2</sup>?

- $W_{periphery} / W_{chip} = o (10 \%)$ ?

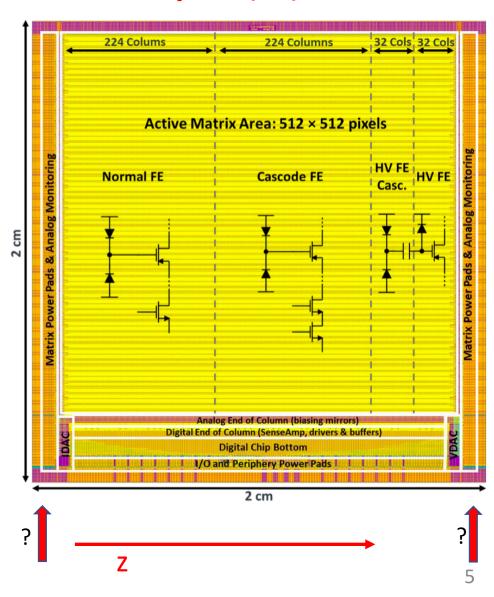

|                                                                   | TJ-Monopix1                       | TJ-Monopix2                                       |  |

|-------------------------------------------------------------------|-----------------------------------|---------------------------------------------------|--|

| Chip Size                                                         | 1x2 cm <sup>2</sup> (224x448 pix) | 2x2 cm <sup>2</sup> (512x512 pix)                 |  |

| Pixel size                                                        | $36\times40~\mu m^2$              | $33.04 \times 33.04 \ \mu m^2$                    |  |

| Total matrix power                                                | 130 mW/cm <sup>2</sup>            | 170 mW/cm <sup>2</sup>                            |  |

| Noise                                                             | ≅11 e <sup>-</sup>                | < 8 e <sup>-</sup> (improved FE)                  |  |

| LE/TE time stamp                                                  | 6-bit                             | 7-bit                                             |  |

| Threshold<br>Dispersion                                           | ≅ 30 e⁻rms                        | < 10 e <sup>-</sup> rms<br>(improved FE + tuning) |  |

| Minimum<br>threshold                                              | ≅ 300 - 400 e <sup>-</sup>        | < 200 e <sup>-</sup>                              |  |

| In-time threshold                                                 | ≅ 350 - 450 e <sup>-</sup>        | < 250 - 300 e <sup>-</sup>                        |  |

| Efficiency at 10 <sup>15</sup><br>n <sub>eq</sub> /cm², 30 μm epi | ≅ 87 %                            | > 97 %                                            |  |

| Efficiency at 10 <sup>15</sup><br>n <sub>eq</sub> /cm², Cz        | ≅ 98.6 %                          | > 99 %                                            |  |

\* Expectations

## TJ 180 nm

## **ALPIDE** 30 mm 1024 x 29.24 um = 29941.76 um Pads over pixels more details in backup Matrix (512 × 1024 pixels) slide **Analog DACs Digital Periphery**

13.76 mm

512 x 26.88 um

## Monopix(2)

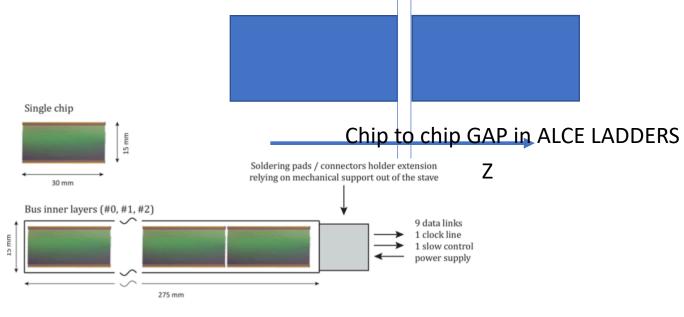

# Assembly procedures for CHIPs HEAD-TO-HEAD in a Module/Ladder

**Table 3.2:** Dimensional requirements for the Pixel Chips.

|                        | Target value       | Variation             |

|------------------------|--------------------|-----------------------|

| Thickness              | $50\mathrm{\mu m}$ | $\pm 5\mu\mathrm{m}$  |

| $\operatorname{Width}$ | $15\mathrm{mm}$    | $\pm 30\mu\mathrm{m}$ |

| Length                 | $30\mathrm{mm}$    | $\pm 30\mu\mathrm{m}$ |

### ALICE CUT-line & thickness requirements

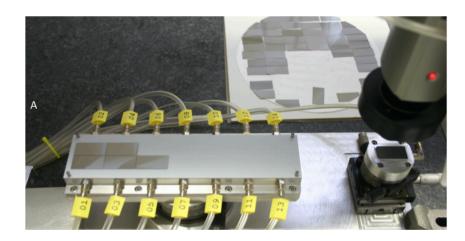

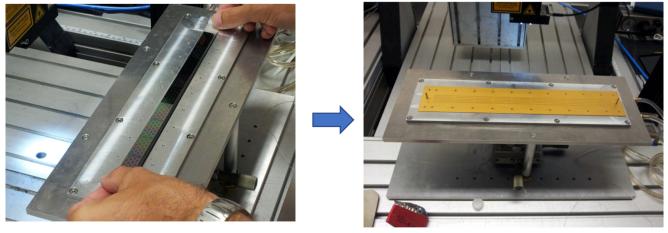

Figure 4.24: Development of the assembly procedure for the OB Module: A) the 14 chips are aligned one after the other in two rows of 7 chips each on a vacuum jig, before they are connected to the FPC and then glued to the Module Carbon Plate; B) first assemblies of dummy Module prototypes.

Figure 6.7: Connections for an Inner Layer Stave.

Figure 4.22: Placement of nine chips on the vacuum table A.

Figure 4.23: Placement of FPC on top of a row of nine chips

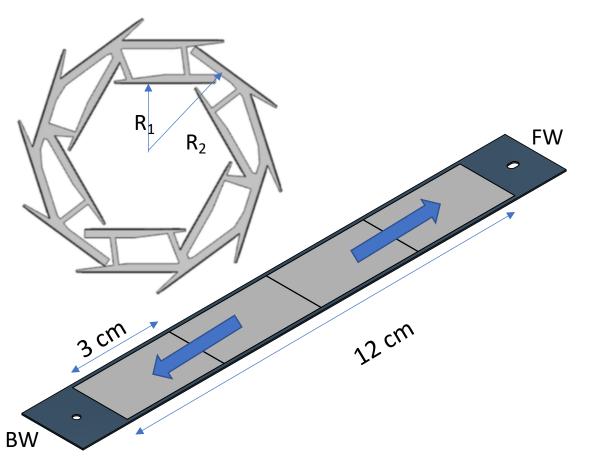

## R&D on iVTX ladder: all-silicon-ladder concept

A single piece of silicon, with a slightly thicker silicon frame and a 40 µm-thin central region:

- L1 and L2 modules identical, placed at R<sub>1</sub>=1.4 cm and R<sub>2</sub>=2.2 cm

- 500 um active-area overlap

- Material budget: 0.1 % X<sub>0</sub>/layer

- Cooling: forced air flow  $(V_{air} \sim m/s)$  for the acceptance region(to be simulated/experimentally demostrated!).

To reach the low-material-target: flex-less module.

L<sub>active</sub> and W<sub>active</sub> o(3 cm) NEEDED!

2 MALTA sensors (TJ-180nm) wire-bonded together

doi-org.in2p3.bib.cnrs.fr/10.1016/j.nima.2020.164895

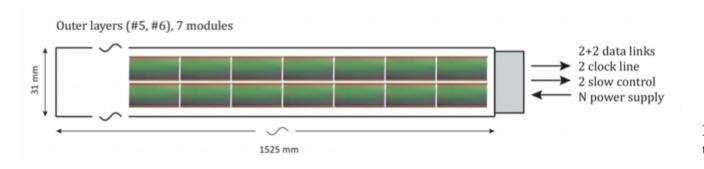

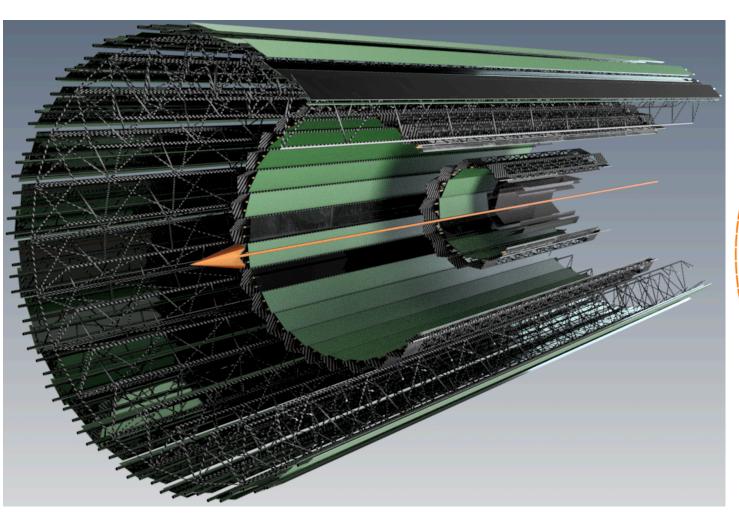

# oVTX spec's (I)

oVTX: L3 and L4

- Material budget: 0.3 % X<sub>0</sub>/layer

- Staves «a la Alice» IB: →

R=3.9/9.0 Length=20/45 cm

- Barrel shaped

- Water cooled sensors

- Operation at room temperature

- Specific power consumption:

- ~ 200 mW/cm<sup>2</sup>

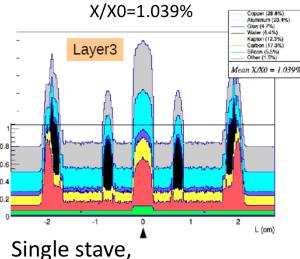

#### ALICE ITS TDR:

Figure 4.2: Prototypes of the Inner Barrel Stave.

Table 4.1: Estimated contributions of the Inner Layer Stave to the material budget.

| Stave element | Component             | Material      | $\begin{array}{c} {\rm Thickness} \\ {\rm (\mu m)} \end{array}$ | $X_0$ (cm) | $X_0$ (%) |

|---------------|-----------------------|---------------|-----------------------------------------------------------------|------------|-----------|

| HIC           | FPC Metal layers      | Aluminium     | 50                                                              | 8.896      | 0.056     |

|               | FPC Insulating layers | Polyimide     | 100                                                             | 28.41      | 0.035     |

|               | Pixel Chip            | Silicon       | 50                                                              | 9.369      | 0.053     |

| Cold Plate    |                       | Carbon fleece | 40                                                              | 106.80     | 0.004     |

|               |                       | Carbon paper  | 30                                                              | 26.56      | 0.011     |

|               | Cooling tube wall     | Polyimide     | 25                                                              | 28.41      | 0.003     |

|               | Cooling fluid         | Water         |                                                                 | 35.76      | 0.032     |

|               | Carbon plate          | Carbon fibre  | 70                                                              | 26.08      | 0.027     |

|               | Glue                  | Eccobond 45   | 100                                                             | 44.37      | 0.023     |

| Space Frame   |                       | Carbon rowing |                                                                 |            | 0.018     |

| Total         |                       |               |                                                                 |            | 0.262     |

|               | ′′0                   |               |                                                                 |            |           |

**'**`(

Single stave, for perpendicular tracks

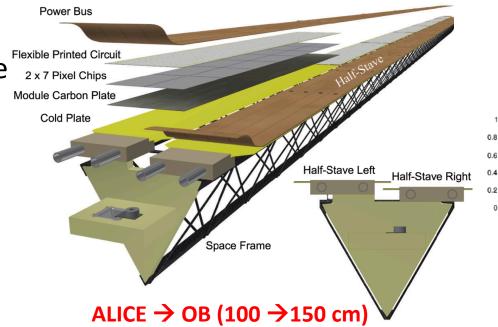

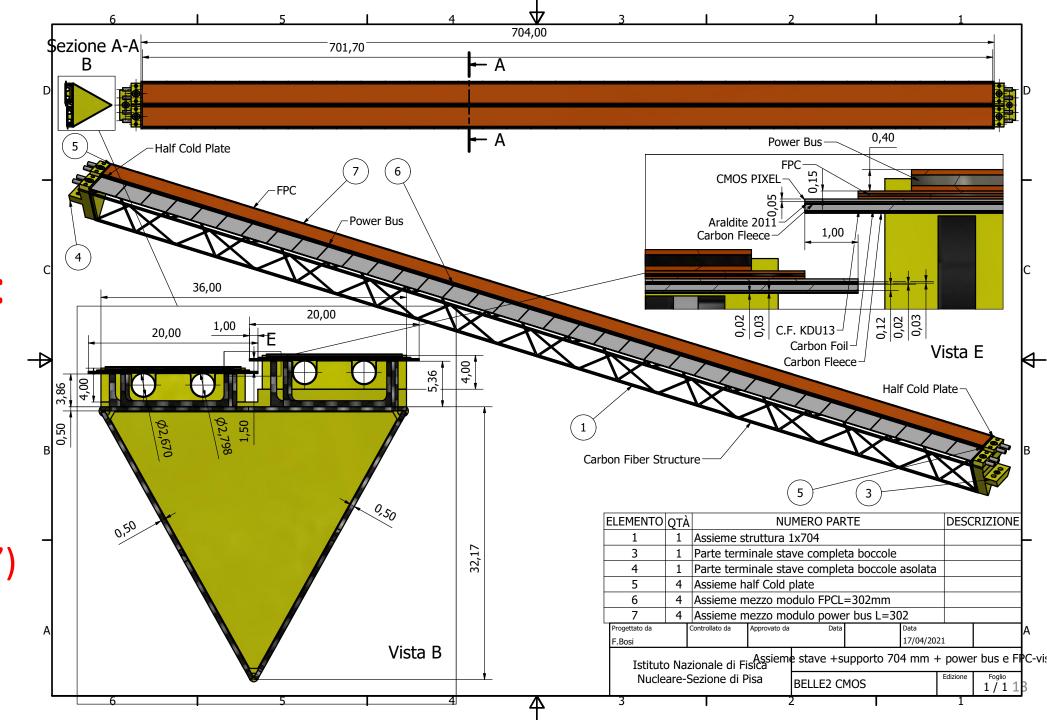

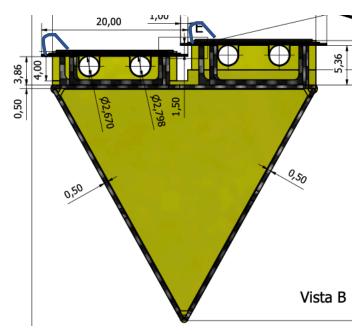

## oVTX spec's (II)

- oVTX: L5

- Material budget: 0.3-0.5 % X<sub>0</sub>/layer

- Staves «a la Alice» OB: →

R = 14 cm Length = 70 cm

- Water cooled sensors

- Operation at room temperature

- Specific power consumption:

- ~ 200 mW/cm<sup>2</sup>

- Power BUS needed?

#### **ALICE ITS TDR:**

Table 4.2: Estimated contributions of the Outer Layer Stave to the material budget.

| Stave element | Component             | Material      | $\begin{array}{c} {\rm Thickness} \\ {\rm (\mu m)} \end{array}$ | $X_0$ (cm) | $X_0$ (%) |

|---------------|-----------------------|---------------|-----------------------------------------------------------------|------------|-----------|

| Module        | FPC Metal layers      | Aluminium     | 50                                                              | 8.896      | 0.056     |

|               | FPC Insulating layers | Polyimide     | 100                                                             | 28.41      | 0.035     |

|               | Module plate          | Carbon fibre  | 120                                                             | 26.08      | 0.046     |

|               | Pixel Chip            | Silicon       | 50                                                              | 9.369      | 0.053     |

|               | Glue                  | Eccobond 45   | 100                                                             | 44.37      | 0.023     |

| Power Bus     | Metal layers          | Aluminium     | 200                                                             | 8.896      | 0.225     |

|               | Insulating layers     | Polyimide     | 200                                                             | 28.41      | 0.070     |

|               | Glue                  | Eccobond 45   | 100                                                             | 44.37      | 0.023     |

| Cold Plate    |                       | Carbon fleece | 40                                                              | 106.80     | 0.004     |

|               |                       | Carbon paper  | 30                                                              | 26.56      | 0.011     |

|               | Cooling tube wall     | Polyimide     | 64                                                              | 28.41      | 0.013     |

|               | Cooling fluid         | Water         |                                                                 | 35.76      | 0.105     |

|               | Carbon plate          | Carbon fibre  | 120                                                             | 26.08      | 0.046     |

|               | Glue                  | Eccobond 45   | 100                                                             | 44.37      | 0.023     |

| Space Frame   |                       | Carbon rowing |                                                                 |            | 0.080     |

| Total         |                       |               | Screenshot                                                      |            | 0.813     |

for perpendicular tracks

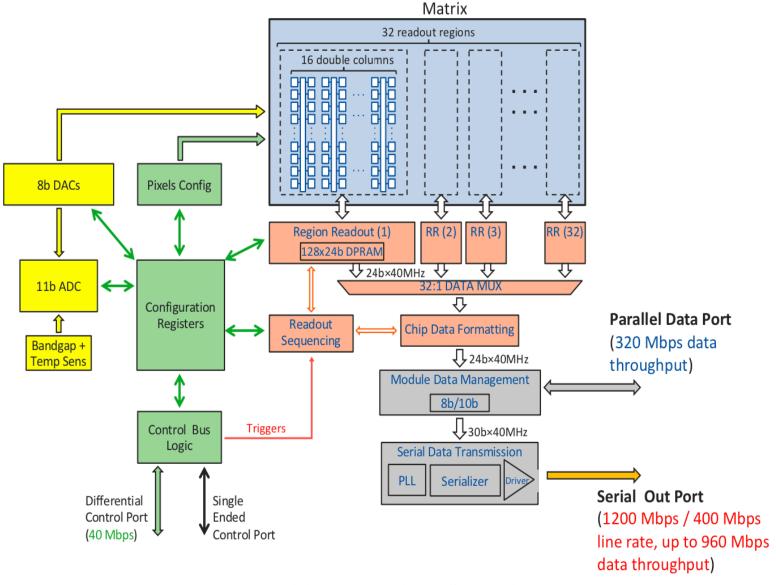

## Input/output pads

(redundancy to be taken into account to cope with chip-failures)

- Power:

- HV +/- (depletion)

- LV +/-

- GND (ref -)

- CMDs: 1 diff. pair?

- CLK: 1 diff. pair?

- Data: 1 diff. pair?

- TRG(?): triggered arch. ?

After Including all the "features":

$$P_{\text{specific}} = ? \quad (< 200 \text{ mW/cm}^2)$$

Is serialisation of the powering needed?

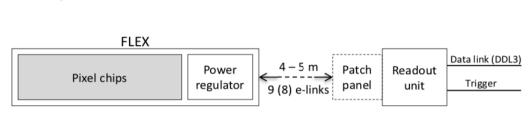

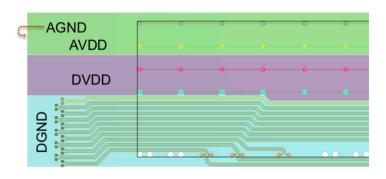

## FLEX CIRCUITS DESIGN

- FLEX introduces a great amount of material  $(\% X_0 \sim \text{comparable to the support structure!})$

- For L1&2 (short) modules smart solution under investigation (flex-less)

- For L3→5 ladders, large number of chips need to be connected and power to be distributed to them: FLEX is mandatory!

- Chip/flex connections: u-bonding.

- Need to make the 1st step in the design of the DAT system!

Figure 6.1: Schematic representation of the read-out path. The number of e-links per Stave is nine for Inner Layers and eight for Middle and Outer Layers.

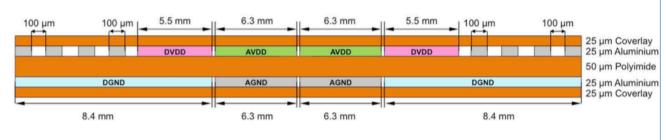

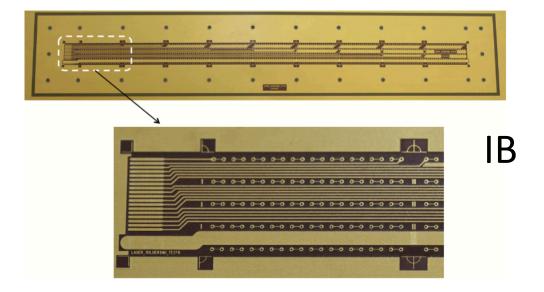

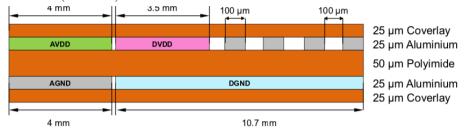

## ALICE (AI) FLEX CIRCUIT

(parallel powering) OB

Figure 4.15: Schematic view of the cross-section (top) and layout (bottom) of the FPC for the OB Stave. The soldering pads for the connection between adjacent FPCs are visibile at the two edges of the layout, the larger rounded pads allow the connections of the PB to the power and ground planes. A differential pair line for data readout that allows to by-pass a Module is also visible at each side edge of the layout.

Figure 4.14: Cu prototype of the FPC for the IB Stave (top) and a close up view of the end-of-Stave section (bottom).

**Figure 4.13:** Schematic view of the stack-up (top) and layout (bottom) of the FPC for the IB Stave.

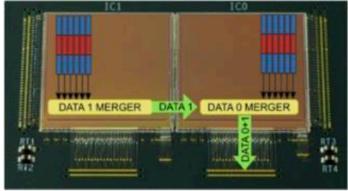

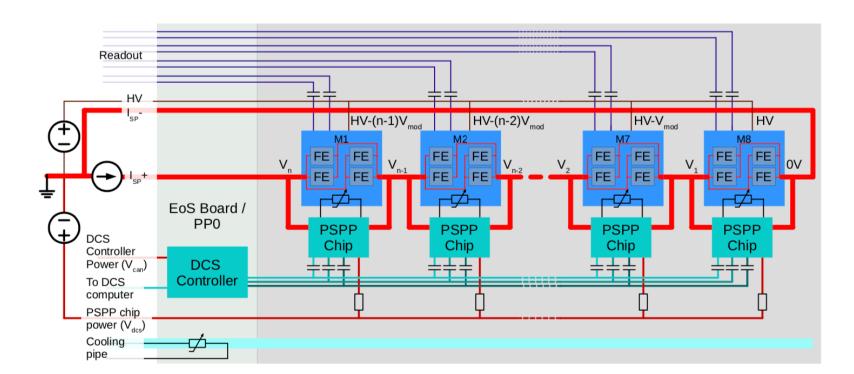

## ATLAS-ITK approach

(CMOS) Drop-in module concept – able to replace hybrid-pixel in terms of the ATLAS TDAQ scheme (interfaced with data aggregator), regulators for (serial) Power, and mechanical compatibility.

From ATLAS ITK TDR

Figure 11.1: Schematic of the Serial Powering distribution on the local support.

Current

Design

of the

L5-ladder

Prototype:

(1st layout exercise with 2cm x 2cm chip, a-la"monopix")

## Mechanics is dressing the chip!

## Chip dimensions affects all the mechanical design:

The functionality of the L1&2 module suggests the chip dimensions.

• We want to refurbish all the VTX with 1! Chip: then the L3,4 &5 staves are

composed/constrained by half-ladders of (chip) width.

Overlaps between adiacent modules, inside each stave and between adiacent staves must cope with dead-regions (W<sub>periphery</sub>)

u-bond connections chip/flex are driven by pad location in the dead region of the chip.

# 5-layer VTX Conceptual Design

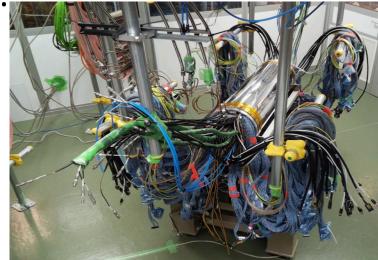

## Remind: the Overall Concept on Connections

- Key-point: reduce ALARA (As Low As Reasonable Achievable!) the amount of services (cables/cooling) to be provided to VTX

- Fast readout (25 ns)/ small pixels, translate in tiny occupancy-> low data rates.

- Warm operation: no isolated lines.

- Possible to reduce cables and connections down to 1/10 of the current VXD (PXD+SVD).

The reduction of services would imply several advantages:

- Simpler integration. Fast exchange if needed;

- Additional room for shielding;

- Less cables in front of the endcaps.

# Backup slides

## **ALPIDE Block Diagram**

## **ALPIDE Pinout**

36