## **OBELIX**

#### DESIGN

### Tomasz Hemperek

hemperek@uni-bonn.de

- In order to share layout we need clear legal situation (Tower + CERN).

- Digital design of Monopix2 can be shared immediately.

We need MoU?

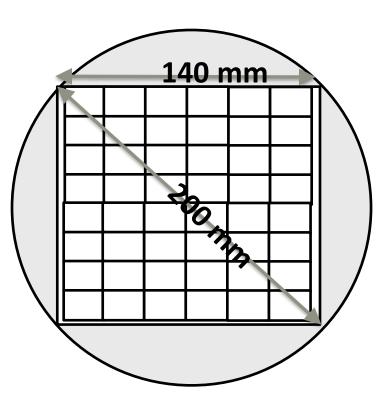

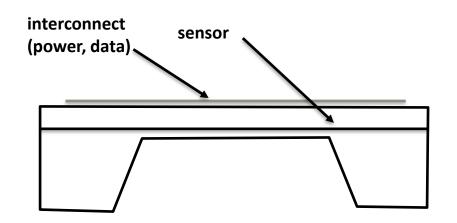

- deposit RDL (1-2 metal system) (up to 5um Cu)

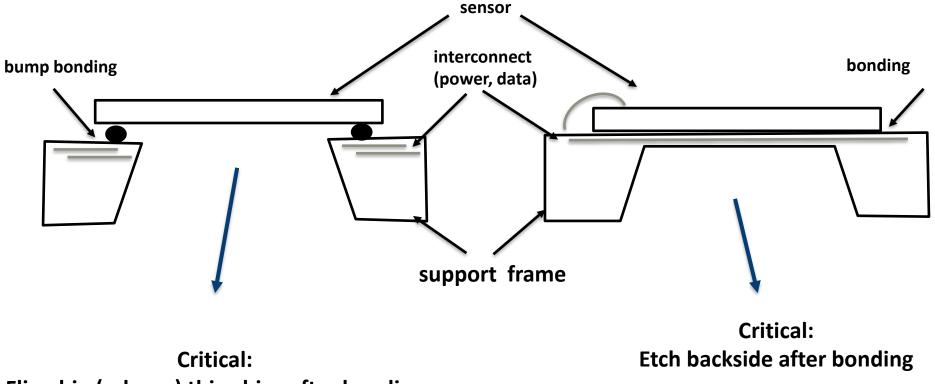

- etch selectively backside

- cut

Need prototype for signal integrity etc. (need wafers)

Flip-chip (release) thin chips after bonding

**Need checking/prototyping**

#### **!ARBITRATY PICTURE FROM INTERNET**

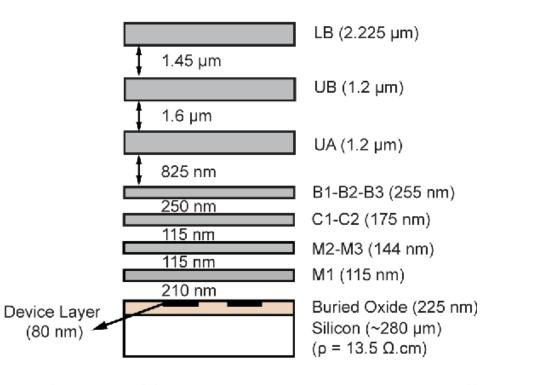

- There are multiple metal options including thick metal Cu, Al, RDL

- Need to know what is available in practice

- Carefully understand and pick most suitable

- Need NDA protected group to disuses this

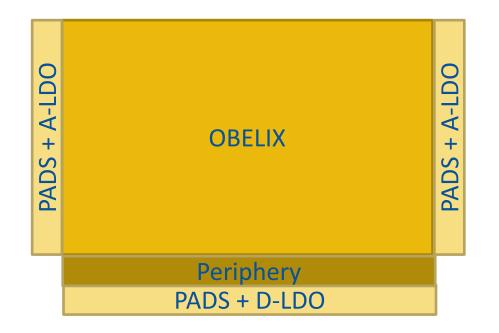

## **Power from the sides**

- Can use design as is\*

- LDO + PADs <~ 150um (ACTION ITEM)

- Power distribution from PADS to matrix

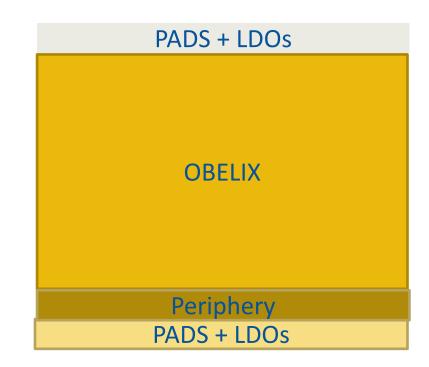

## **Power from bottom/top**

- Mayor pixel redesign needed

- Metal stack choice is critical

- ACTION ITEM: investigate voltage drop dependence on pixel/threshold)

# **Group chat**

## https://chat.belle2.org/channel/vtx\_upgrade\_obelix