### CPPM DepCMOS dvp -interests in OBELIX design-

May 12th 2021

Marlon Barbero

## LF150 project

### **LFOUNDRY 150nm technology**

### CPPM: Implication since 2012

### LF-MONOPIX2 circuit (Bonn, CPPM, IRFU)

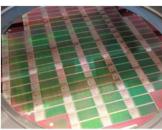

Sent for fabrication June 2020 (tests started Feb.2021) : 12 wafers

- will request for 2 wafers with standard passivation with polymide

- remaining 10 wafers with "special" passivation, in order to have higher temperature tolerance for backside processing

### + Test Structures :

Small pixel pixels ( $50\mu \times 50\mu$ ), Bandgap, Guard Ring tests, APD PCB done and produced.

### **On-going**:

- LF-Monopix2 Card dvp by Bonn (2 setups in CPPM).

- LF-Monopix2 tests have started, Bonn and CPPM.

- 1<sup>st</sup> positive tests on LF-Monopix2 (CPPM/Bonn).

- Wirebonding of tests structures on-going  $\rightarrow$  1<sup>st</sup> tests soon.

CPPM DepCMOS Pixel, Marlon Barbero, May 12th 2021

# TJ180 project

### **TJ 180nm CIS technology**

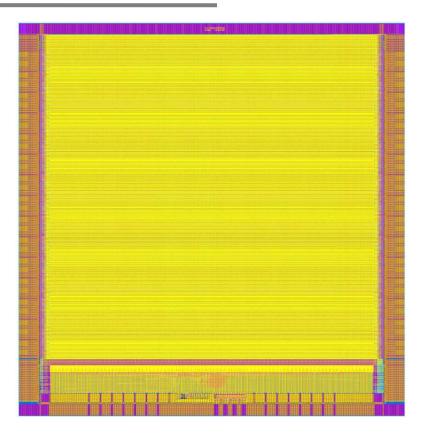

### CPPM: Implication since 2016 **TJ-MONOPIX2** (CERN, Bonn)

#### Sent for fab Nov 2020 (tests started in March)

Bonn test bench (firmware, carte, software). CPPM:

Getting ready for testing the circuit Test bench mounting on-going (synergies LF150 and TJ180 testing)

Wire-bonding tries with local compagny

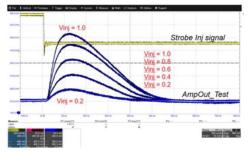

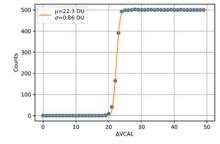

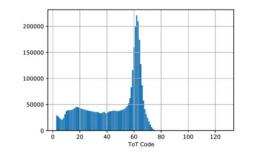

#### 1<sup>st</sup> positive tests (Bonn):

CPPM also has a TJ 65 nm implication  $\dots$  1<sup>st</sup> designs done in 2020

CPPM DepCMOS Pixel, Marlon Barbero, May 12th 2021

### Team plans / support

- DepCMOS: developped in CPPM for ATLAS L4, interest for Future Colliders and BelleII upgrade.

- Support from DICE IN2P3 master project + AIDAinnova.

- Team:

- Manpower:

- Testing TJ / LF / test structures:  $\sim$ 1.5-2 FTE

- Experience with: Monopix series, tests in lab, tests under radiation, SEU test...

- Design TJ180 OBELIX: ~1-1.5 FTE

- Experience with: TJ technology ; design ShuntLDO / SEU hard cells (DICE, TRL...)

- Interests in OBELIX:

- LDO, SEU-hard cells + analog FE, Bias DACs...

- Cliosoft management, participation to integration, floorplanning, simulation ...

CPPM DepCMOS Pixel, Marlon Barbero, May 12th 2021