Belle II Trigger/DAQ Workshop 2022 2022/11/30 (Wed)

# VXD TRG R&D status

The University of Tokyo

Tomoyuki Shimasaki

#### L1 rate will reach DAQ limit @ L ~ $10 \times 10^{34}$ (with DAQ limit ~ 20kHz) Reduction of L1 rate is needed

| Category      | Bit                                       | Exclusive<br>rate (kHz)<br>@L=4.5e <sup>34</sup> | Exclusive<br>rate (kHz)<br>@L=9e <sup>34</sup> | Exclusive<br>rate (kHz)<br>@L=18e <sup>34</sup> | Exclusive<br>rate (kHz)<br>@L=54e <sup>34</sup> |

|---------------|-------------------------------------------|--------------------------------------------------|------------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| CDC           | ffy                                       | 1.8                                              | 3.6                                            | 7.2                                             | 21                                              |

| standard bits | fyo                                       | 0.6                                              | 1.2                                            | 2.4                                             | 7                                               |

| ECL           | c4                                        | 0.26                                             | 0.5                                            | 1.0                                             | 3                                               |

| standard bits | hie3                                      | 0.8                                              | 1.6                                            | 3.2                                             | 9                                               |

| KLM τ/dark    | klmb2b, eklmb2b, beklm<br>cdcklm, ecleklm | 0.23                                             | 0.23                                           | 0.23                                            | 0.23                                            |

|               |                                           | 0.36                                             | 0.7                                            | 1.4                                             | 4                                               |

| CDC τ/dark    | stt                                       | 1.37                                             | 2.8                                            | 5.6                                             | 17                                              |

|               | syo                                       | 0.10                                             | 0.2                                            | 0.4                                             | 1                                               |

|               | fy30                                      | 0.18                                             | 0.4                                            | 0.8                                             | 2                                               |

| Subtotal      | OR of above bits                          | 5.7                                              | 11                                             | 22                                              | 66                                              |

| ECL τ/dark    | Iml                                       | 0.54                                             | 1.0                                            | 2.0                                             | 6                                               |

|               | eclmumu                                   | 0.51                                             | 1.0                                            | 2.0                                             | 6                                               |

| Total         | OR of all bits                            | 6.7                                              | 13                                             | 27                                              | 80                                              |

T. Koga(KEK), 2022/7/21

#### **Motivation**

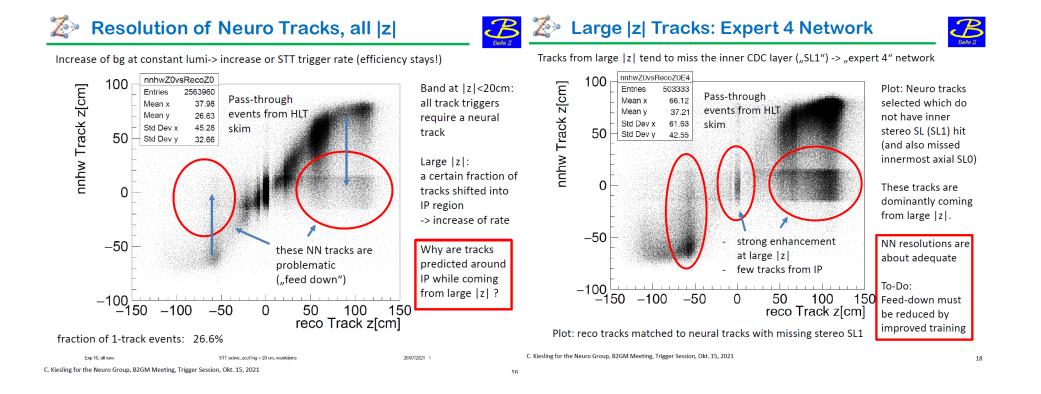

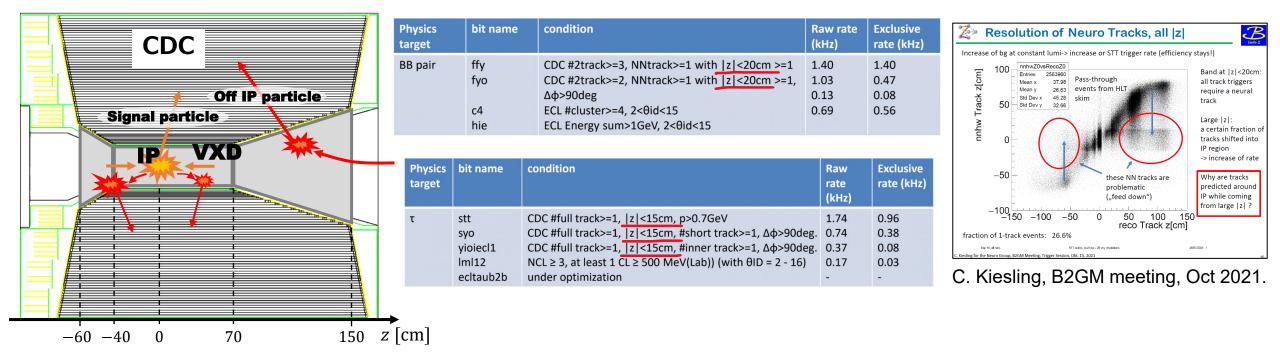

- CDC trigger has highest trigger rate among sub-triggers of Belle II L1 trigger.

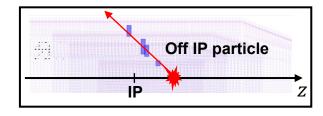

- Off IP particles are major beam-background source.

- CDC trigger rejects particles coming only from 15 or 20cm away from the IP.

# Since the z resolution of current CDC trigger is insufficient, there is room to improve the current L1 trigger

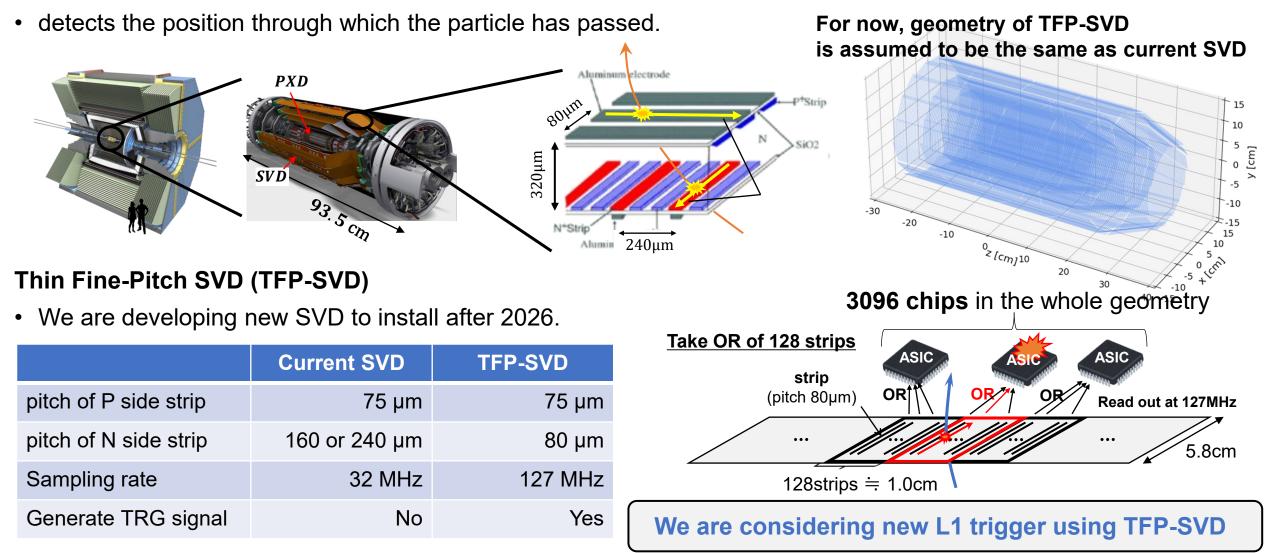

### **TFP-SVD**

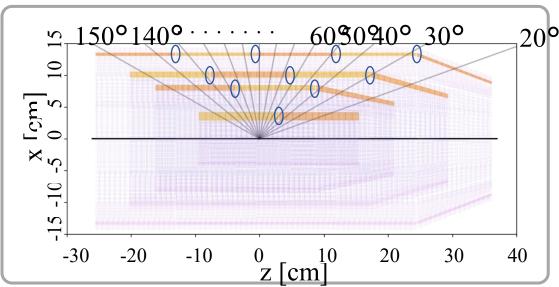

#### SVD

• the double-sided silicon-strip detector located in the innermost part of Belle II detector.

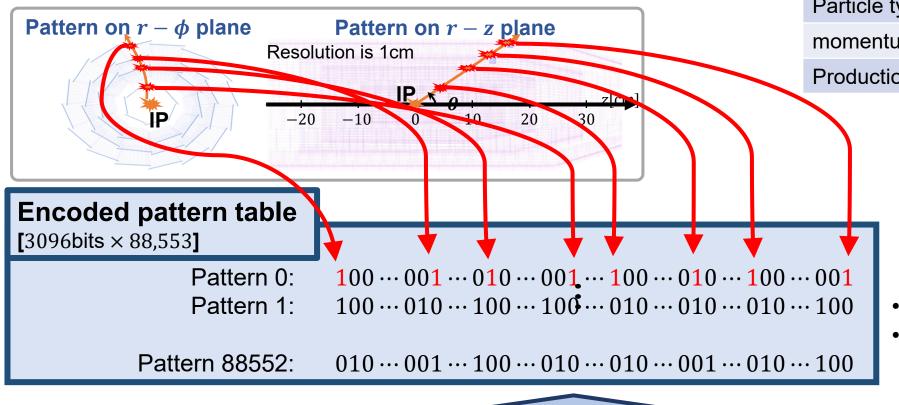

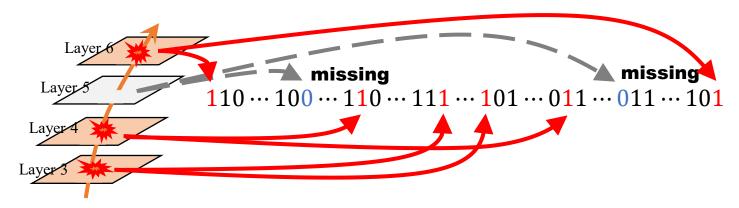

# **Development of core logic: Pattern table**

#### Pattern matching by LOOK UP TABLE (LUT)

• Collect track patterns of particles from the IP.

**Online hits:**

#### **Conditions of particle generation for LUT**

| Parameter                 | Condition           |  |

|---------------------------|---------------------|--|

| Particle type             | $\mu^{\pm}$         |  |

| momentum <i>p</i> [GeV/c] | $0.2 \le p \le 3.0$ |  |

| Production point z [cm]   | z = 0               |  |

#### distinguish Off-IP track

- # of track pattern:88,553

- Each track is encoded in bit string with 3096-width

110 ··· 101 ··· 110 ··· 111 ··· 101 ··· 011 ··· 111 ··· 101

ex) this hits include the track pattern 0 of the table, and TFP-SVD trigger issue a trigger

Compare online hits with the table

# **Modification of core logic**

- There are sensor dead area at the edge of sensors.

- If a particle pass through the gaps, the track cannot be found by above algorithm → trigger efficiency drops at the dead areas

• For high trigger efficiency, matching condition is relaxed so that online hits can match the pattern table even if a particle doesn't hit any one of the four layers.

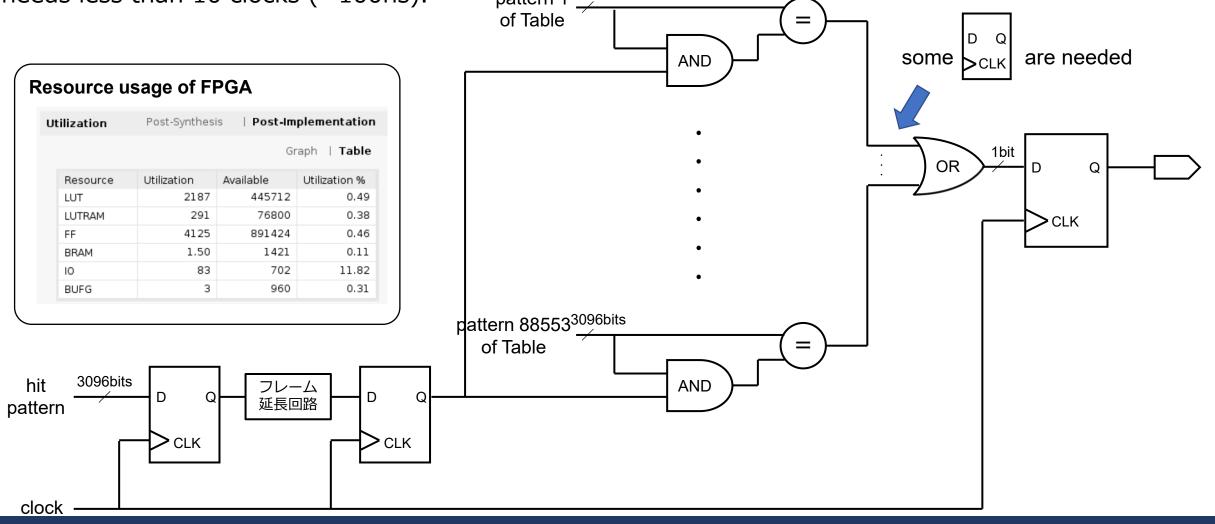

## **Implementation of logic on FPGA**

- We implemented core logic on FPGA

- 88553 patterns of the table are written in registers.

- It needs some flip flops to take the logical OR of results of 88553 equivalence operations → Core logic needs less than 10 clocks (~100ns).

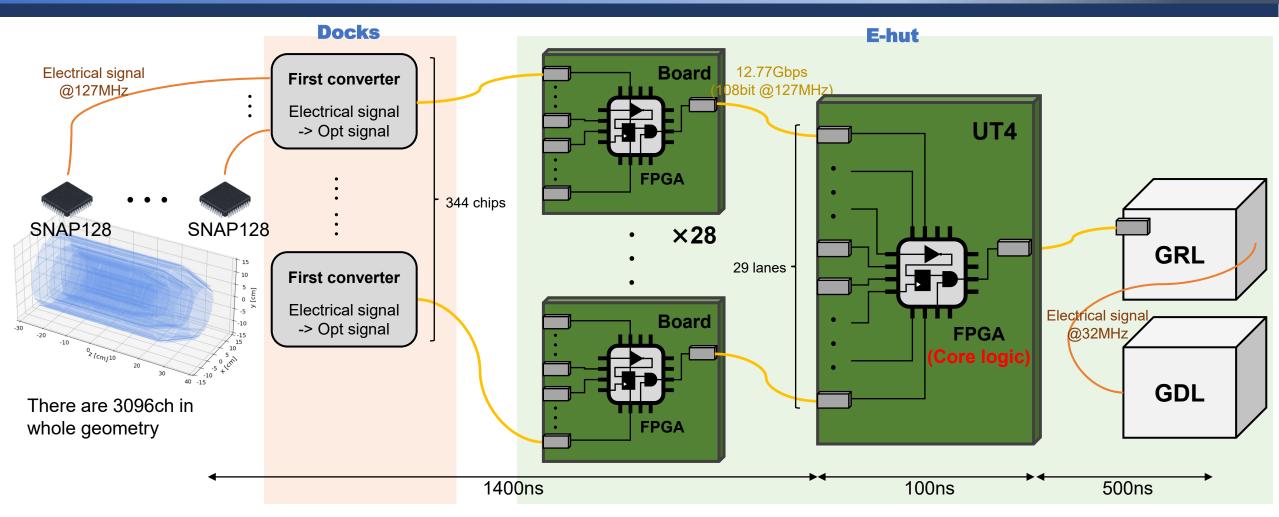

#### **Firmware setup**

- We are assuming that it takes about 1400ns to convert electrical signals to optical signals and transmit the optical signal to UT4(core logic) via optical fiber cables.

- The core logic takes about 100ns (5% of total trigger latency).

- It takes about 500ns to transmit the TFP-SVD trigger output to GDL.

- After all, trigger latency to the GDL is about 2000ns(=1400+100+500).

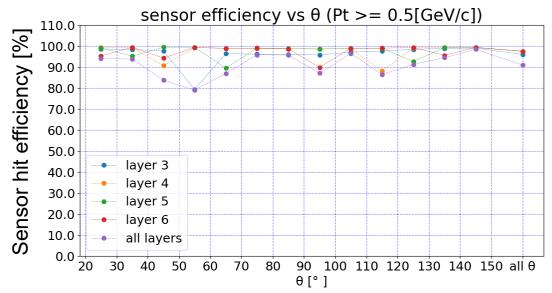

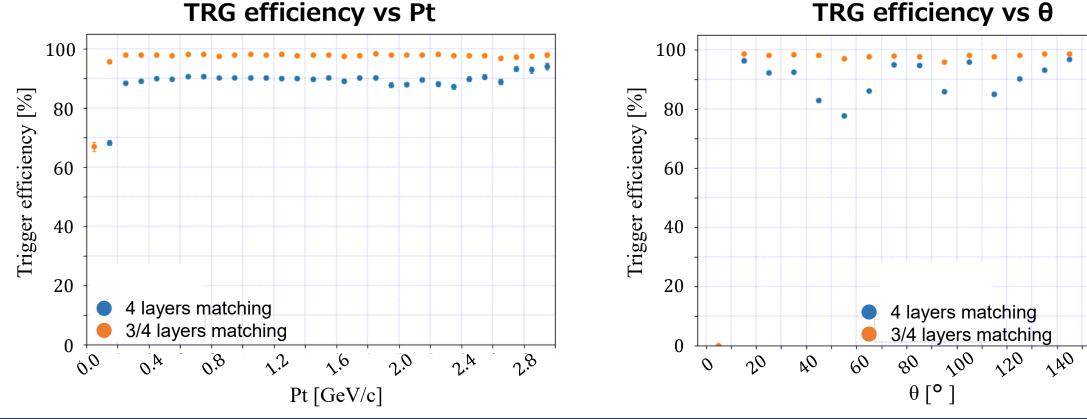

# **Performance on simulation: On-IP particle study**

We generated only one particle at the IP and investigated trigger efficiency.

Blue (orange) plots represents trigger efficiency of 4 layers (3/4 layers) matching.

- is about 90% for all Pt.

- has dependency on  $\theta$ . trigger efficiency drops where there are gaps.

- is about 98% for all Pt and  $\theta$ . Relaxation of matching condition is effective against the existence of gap.

Ζ

160

280

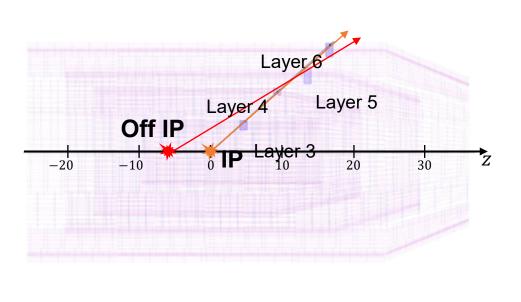

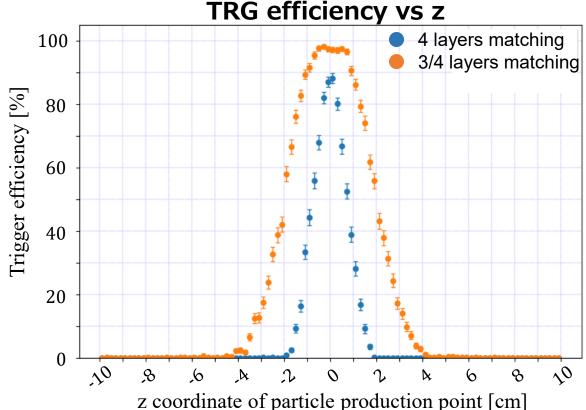

# **Performance on simulation: Off-IP particle study**

- To investigate Off-IP particle rejection power, we generated only one particle at various z.

- can reject particles generated at 2cm away from the IP with a probability of more than 99%.

- can reject particles generated at 4.5cm away from the IP with a probability of more than 99%.

- slow decrease in graph is due to relaxation of matching condition

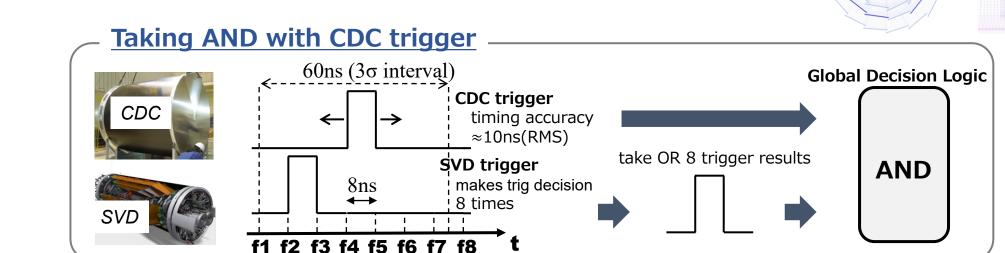

- BG particles with low momentum can make a lot of hits → we investigated fake trigger probability @ nominal L

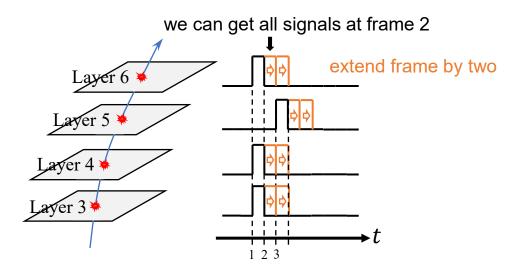

- We considered two types of time scale

- Sampling rate of ASIC of TFP-SVD: 8ns

- Timing accuracy of CDC trigger: 60ns

• As shown in table below, fake trigger prob of 3/4 layers matching is high. Some countermeasures are needed.

#### TRG Prob

|                             | 4 layers matching | 3/4 layers matching |

|-----------------------------|-------------------|---------------------|

| 8ns (per one frame)         | 0.67%             | 10.84%              |

| 60ns (taken OR of 8 frames) | 2.44%             | 35.84%              |

#### Summary

- We considered firmware setup and developed core logic of TFP-SVD trigger.

- The total latency is about 2µs, and the latency of core logic is about 100ns(5%).

- Core logic can be implemented in one UT4 board.

- Trigger performance on simulation in shown table below.

- 3/4 layers matching algorithm with high trigger efficiency and sufficient Off-IP rejection power (current rejection area: large |z| > 15cm) is better.

#### Trigger performance on simulation

|                                      | 4 layers matching | 3/4 layers matching |

|--------------------------------------|-------------------|---------------------|

| Efficiency                           | 90%               | 98%                 |

| Fake TRG prob under random BG (60ns) | 2.44%             | 35.84%              |

| Off IP rejection are                 | z  > 2cm          | z  > 4.5cm          |

#### To Do

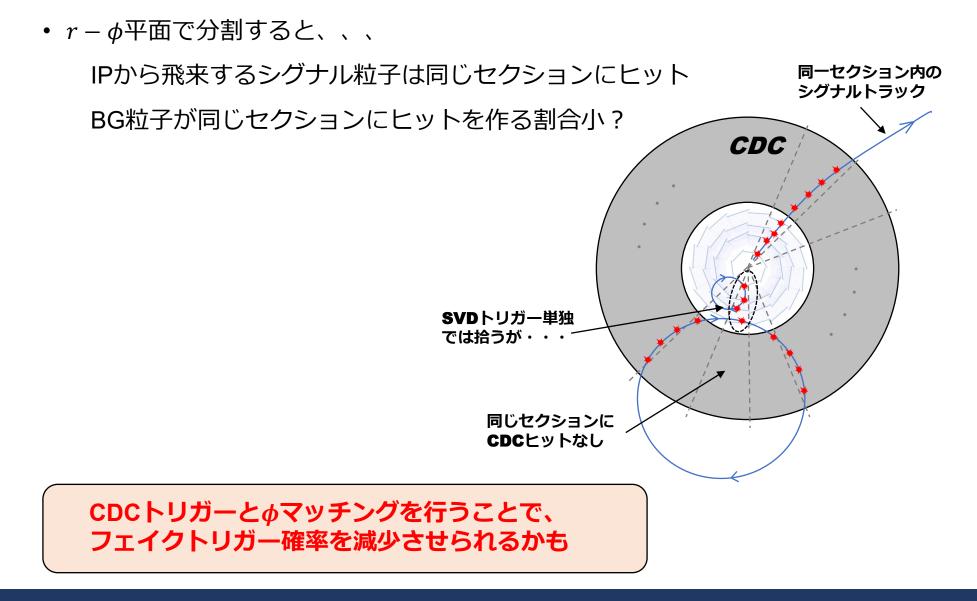

- For random BG, we will consider matching of TFP-SVD and CDC.

- We will calculate how much this TFP-SVD trigger improve trigger rate.

# **BACK UP**

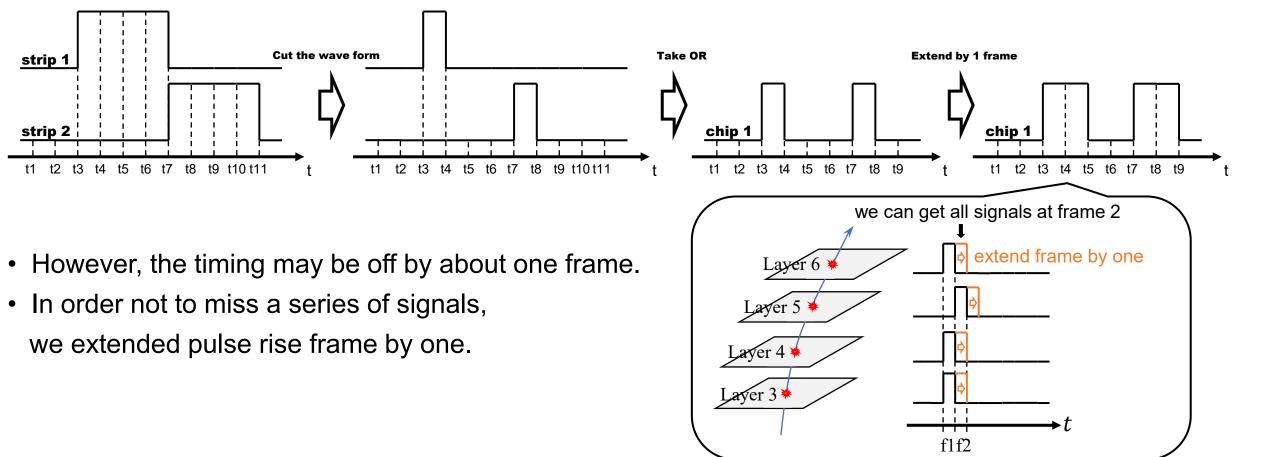

### Wave form shaping

#### Read out by ASIC

- One ASIC of TFP-SVD(SNAP) will read out signals every about 8ns and will take OR.

- The timing of particle going through a sensor can be obtained from the rising edge of wave form.

13 / 11

• For that, before taking OR, we cut the waveform leaving rising edge.

ビームバックグラウンドはφ方向ランダムにセンサーを鳴らすと考えられる.

ska2:BMHDCCT:CURR ska2:BMHDCCT:CURR BZ\_nsmiget:1k3ugL: BZ\_nsmiget:1k3ugL: 1400 1200 陽電子ビームのみの運転期間 電子ビームのみの運転期間 1000 CDCトリガー(bit"stt")のレート 1 陽電子ビーム電流 ₽ 800 ----[mA, 600 陽電子ビーム電流 400 1 I 200 Т Т 16:00 14:00 Jun 16, 2021 15:00 17:00 18:00 19:00 . 1