TRG upgrade 2022/12/2 T.Koga

## Motivation

- -TRG upgrade plan in LS2 and beyond

- -VXDTRG

- -CDCTRG

- -ECLTRG

- -Increase latency

- -(UT5)

## VXDTRG

-With VXD upgrade, we can implement VXDTRG

-Purpose: beamBG rejection with |z| measurement

-<u>R&D</u> of VXDTRG logic is on-going with TFP-SVD by Shimasaki-san

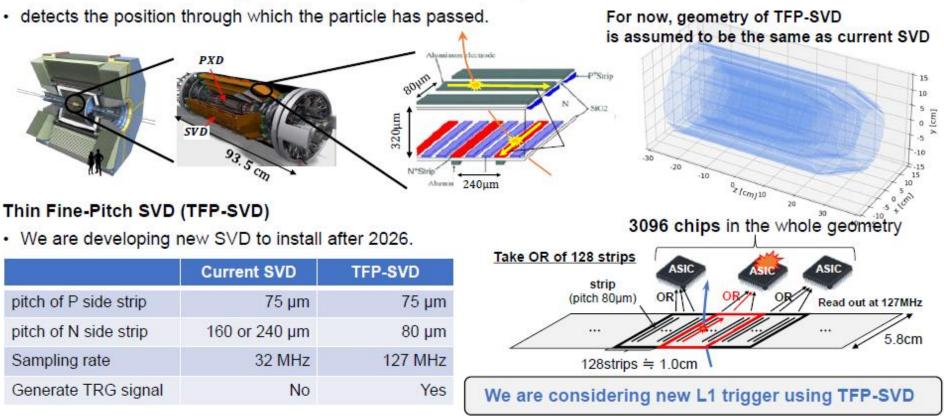

#### SVD

· the double-sided silicon-strip detector located in the innermost part of Belle II detector.

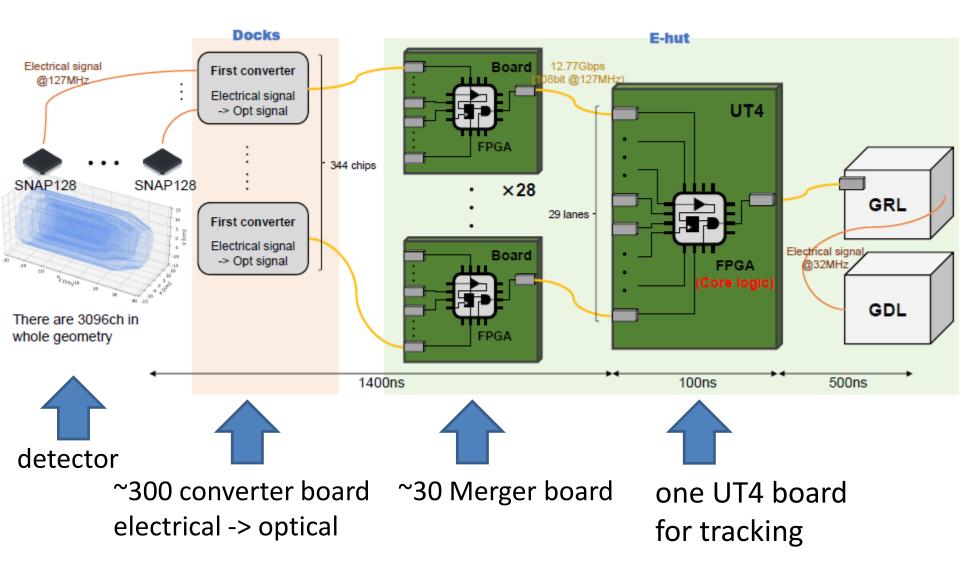

## VXDTRG dataflow

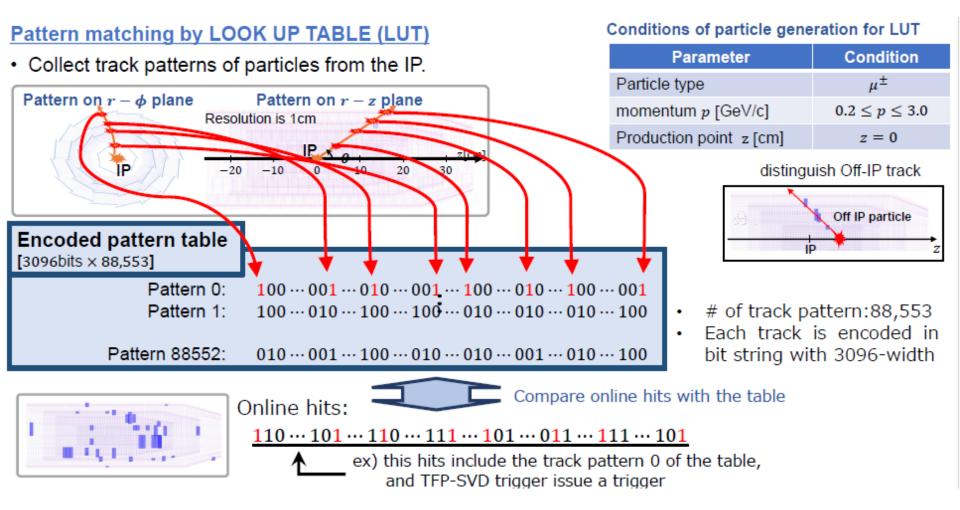

## VXDTRG track reconstruction logic

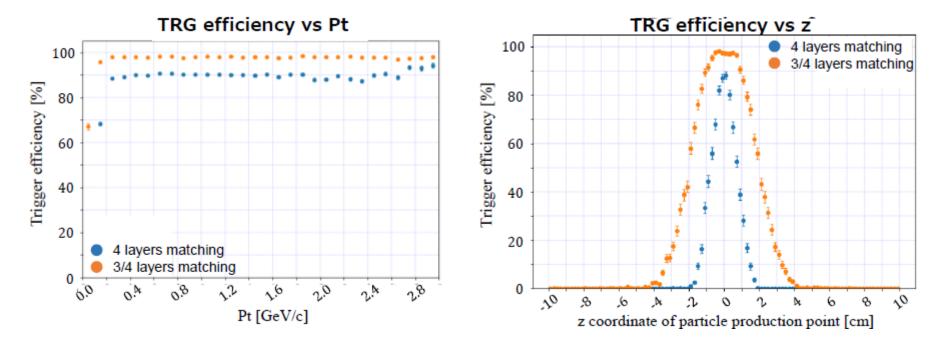

## VXDTRG expected performance

-Tracking performance is studied with a particle gun -High efficiency

-|z|< 2~4cm cut can be applied

-Fake track probability is studied with beamBG MC -~1% fake track per 8ns with 4 layer matching -~10% fake track per 8ns with 3 layer matching

## CDCTRG

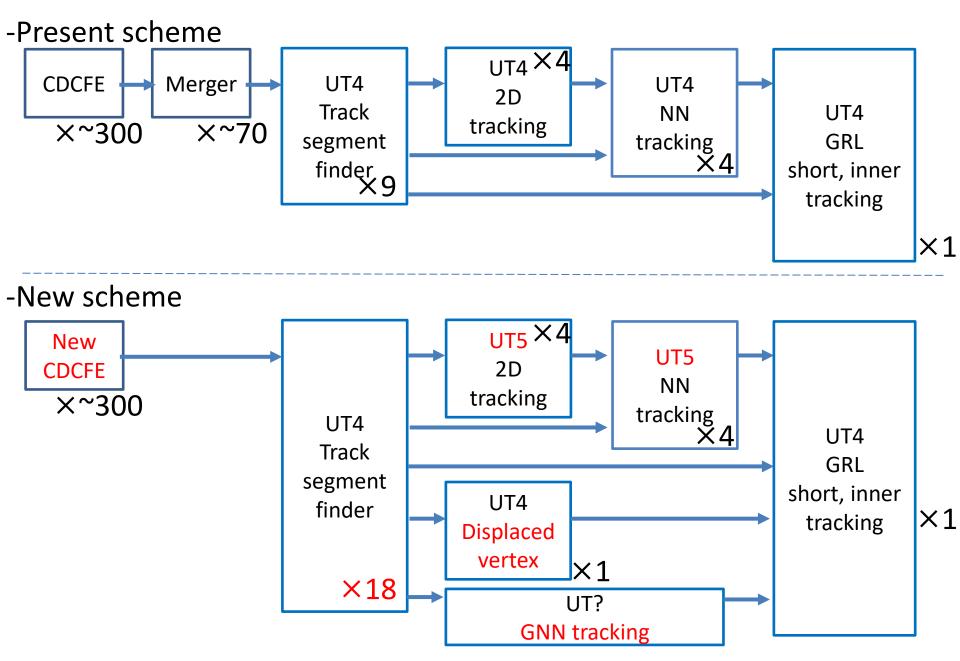

# Upgrade of CDCFE and CDCTRG

-Optical transceiver speed will be improved with new CDCFE -To use the high speed, receiver side (MGR) need to be upgraded too ->We plan to bypass the MGR and connect TSF directly

|                     |                 | speed per lane                                                                                                                                                  | #lane per<br>CDCFE<->TRG | #bit/32MHz/CDCFE                                                                                                                                             |

|---------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Present CDCFE       |                 | 3.2Gbps<br>(2.5Gbps with 8b10b)                                                                                                                                 | 4                        | 256                                                                                                                                                          |

| New CDCF            | E               | 10.3Gbps<br>(10Gbps with 64b66b)                                                                                                                                | 2                        | 512                                                                                                                                                          |

|                     | Present         | configuration                                                                                                                                                   | New configu              | ration                                                                                                                                                       |

| 1 boards<br>9 links | ↓<br>Event Time | Front-end<br>GTP<br>Merger<br>GTX<br>GTX<br>GTX<br>SF<br>Sounds<br>292 boards<br>292 links<br>9 boards<br>70 links<br>GTH<br>2D Tracker<br>4 boards<br>36 links |                          | Front-end<br>292 boards<br>1168 links<br>584 links<br>584 links<br>UT4 20 boards<br>TSF<br>9 boards<br>70 links<br>GTH<br>2D Tracker<br>4 boards<br>36 links |

|                     |                 | GTH<br>3D Tracker 8 boards<br>8 links                                                                                                                           |                          | GTH<br>3D Tracker 8 boards 8 links 8                                                                                                                         |

#### Merit of high speed

-With the higher speed, we can send TDC and ADC of all wires to CDCTRG

29 28 27 26 25 24 23 22 21 20

Figure 10: Part of CDC outer SL inside wire cell configuration [6].

#### Data from a CDCFE to CDCTRG

|         | data                                                                                                                                                                                 | #bit/32MHz/CDCFE                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Present | <ul> <li>-hitmap of 5/6 wires</li> <li>-tdc of part(~1/6) of wires (2ns)</li> <li>-fastest tdc among all wires</li> <li>-edge information</li> <li>-clock</li> <li>-total</li> </ul> | 48 (40)bit<br>5bit × 16wire=80<br>5bit × 16wire=80<br>10bit<br>9bit<br>227bit < 256bit |

| New     | <ul> <li>-hitmap of all wires</li> <li>-tdc of all wires (2ns)</li> <li>-adc of all wires (4bits)</li> <li>-clock</li> <li>-total</li> </ul>                                         | 48bit<br>5bit × 48=240<br>4bit × 48=192<br>9bit<br>489bit < 512bit                     |

## Upgrade of trackers

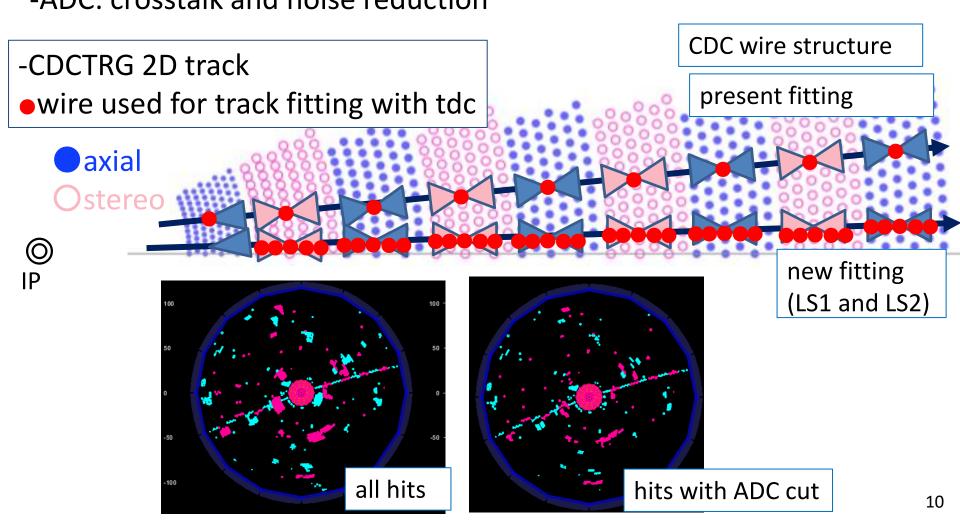

With the higher speed, we can send TDC and ADC of all wires to CDCTRG

Great potential for BG reduction and efficiency improvement for future

TDC: increase fitting points (x5) to improve z resolution

ADC: crosstalk and noise reduction

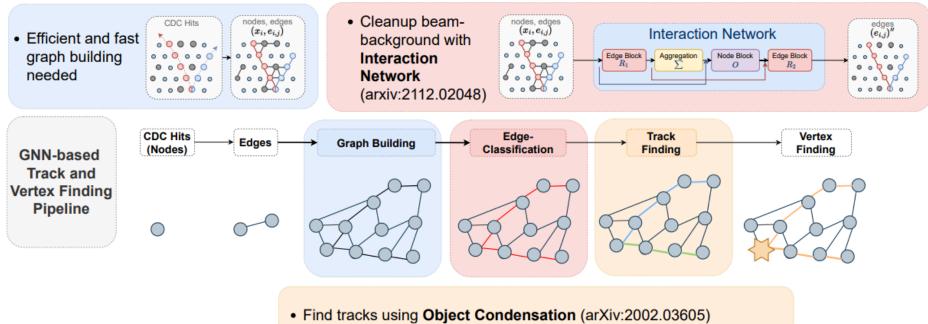

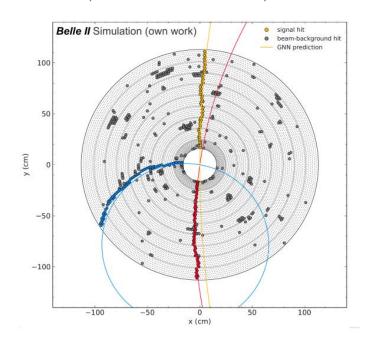

#### CDCTRG GNN

#### -<u>Lea</u> and <u>Philip</u> started R&D of tracking and vertex finding with Graphical neural network

-With CDC wire, track finding, fitting and vertex finding are performed.

• Goal: predict Track Fitting parameters and find condensation points

## CDCTRG GNN

#### -Training and performance evaluation are on-going at offline at first, without think of level1 trigger constraint (all CDC hits, ADC, TDC are used without considering latency and FPGA)

| Found Tracks in Event                                    | GNN (offline) <sup>a</sup> | TRGCDC2DFinderTracks | TRGCDCNeuroTracks | RecoTracks |

|----------------------------------------------------------|----------------------------|----------------------|-------------------|------------|

| Only signal tracks                                       | 91.5%                      | 94.0%                | 93.8 %            | 90.6 %     |

| Missing signal tracks                                    | 2.1 %                      | 5.6 %                | 5.6 %             | 0.02 %     |

| All signal tracks and additional tracks <sup>a</sup>     | 5.9 %                      | 0.4 %                | 0.6 %             | 9.38 %     |

| Missing signal tracks and additional tracks <sup>b</sup> | 0.5%                       | 0.01%                | 0.0 %             | 0.005 %    |

| Per Track                                                |                            |                      |                   |            |

| Efficiency                                               | 97.4%                      | 94.4%                | 94.4%             | 99.98%     |

| Precision                                                | 95.8 %                     | 99.8%                | 99.7%             | 93.3%      |

- -The offline tracking looks succeeded

- -Plan to consider how to implement the logic to FPGA

# ECLTRG

#### -Unno-san's talk

- -During LS1, we plan to do performance evaluation of ECLTRG with future high luminosity and BG by using MC

- -Investigate possible issues, and determine long term upgrade plan to solve the bottolneck.

- Background study

- BGOverlay logic for both MC and random data

- Performance study for MC and data

- Consistency study between MC and data

- Based on the results, make a strategy for high luminosity and bkg conditions (for both after LS1 and LS2)

### ECLTRG plan after LS1 and in LS2

- Try to separate two energy deposition in one TC (if necessary) ?

- If two signal peak positions are >500ns, it would be possible

- New ShaperDSP ?

- Currently 576 ShaperDSPs in 52 9-VMEs around Belle2 detector

- Alex is planning to upgrade ShaperDSP

- · Some studies are in progress in BINP (the status not shown anywhere)

- · For ecl trigger, any requests and the meaningful improvement ?

- "TC" timing can be improved if cell-by-cell timing adjustment in each TC is possible, but bad resolution is mainly from low energy TC

- · Any merit if logic of FAM can be implemented in new ShaperDSP ?

- TC with from 4x4=16xtail to 2x2 if it improves some performance?

## L1 Latency

-Present L1 latency is limited by SVD

->If VXD is upgraded, we can enlarge latency.

If ~1µs latency increases, we can implement a UT4 for new logic.

#### -<u>Next bottolneck</u> is KLM RPC, ~5.2µs.

-FPGA resource of SCROD is occupied, and we are not sure if buffer size can increase or not (at present there is no FW expert)

-Need dedicated study, or upgrade of electronics.

| Detector | Maximum L1 latency                                                                                                                                                                                    | Contacted Expert                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| PXD      | %Rough estimation<br>~3times larger than now.<br>At present 50 look back (unit=104ns) is used, it may go up to 191.                                                                                   | Bjoern Spruck                       |

| SVD      | 5.0µs (now)<br>~10µs in future with the upgrade of detector and FE                                                                                                                                    | Katsuro Nakamura                    |

| CDC      | ~15µs+more, depending on FPGA resource and IP core                                                                                                                                                    | Yu Nakazawa                         |

| TOP      | ~9µs tested, just under 1 accelerator revolution = 10 µs should be possible, maybe 12 µs with larger FW changes. More would be very difficult without hardware upgrade, ring buffer has limited size. | Martin Bessner                      |

| ARICH    | At present 56clk (1clk=15.7ns) depth buffer is used.<br>The depth can increase depending on FPGA resource. We tested 112clk depth, it looks fine.<br>Thus, 10~15 us latency is possible.              | Yun-Tsung Lai, Kenta Uno            |

| ECL      |                                                                                                                                                                                                       | Mikhail Remnev, Alexander<br>Kuzmin |

| KLM      | 16µs for scintillator<br>5.2µs for RPCs, need confirmation                                                                                                                                            | Christopher Ketter                  |

# Summary

-TRG upgrade plan in LS2 and beyond

-VXDTRG

-add VXD to TRG with upgrade of VXD

-CDCTRG

- -send ADC and TDC of all wires from new CDCFE to CDCTRG

- -update of tsf, trackers

- -GNN based tracking approarch

#### -ECLTRG

- -perform simulation study for future high luminosity and BG during LS1 to consider possible upgrade in LS2

- -with new shaper DSP, smaller size of TC can be used to get cluster shape

-Increase latency

-SVD is present bottolneck and KLM is the second. Need investigation for KLM.

# backup

-

-https://indico.belle2.org/event/1307/sessions/378/attachments/3070/5670/mmilesi\_ECLPid\_B2SKW\_2020.pdf

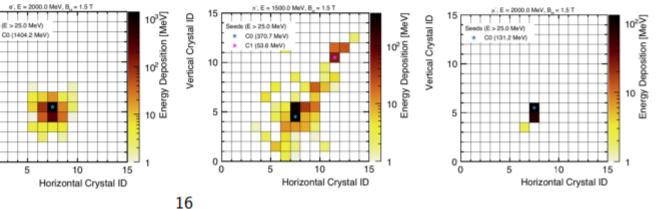

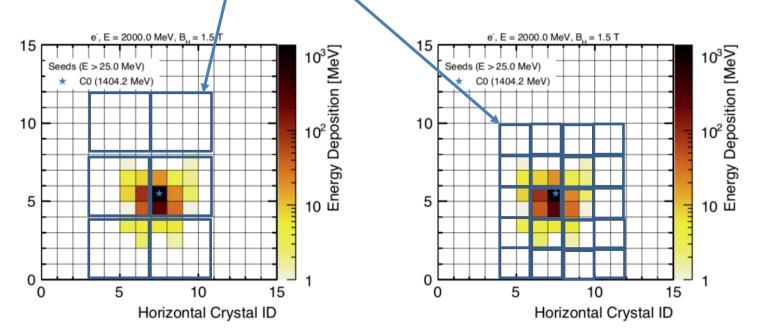

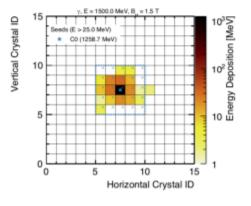

#### 4. Overview of ECL clustering

Simulation of single particles' energy deposition in a 15x15 ECL crystal array (pre-clustering):

#### γ

- Radially symmetric shape

- Usually contained in

5x5 cells

#### • Similar shape of $\gamma$

е

Less symmetric

15

10

0

(*B* field bend, brems  $\gamma$  emitted before the ECL)

- Ionisation loss contained

- in 1-2 cells.

- Asymmetric lateral spread

#### due to hadronic interactions

π

#### μ

- Pure MIP behaviour.

- <*E*<sub>cluster</sub>> ~ 200 MeV