# FTSW4 development status

Mikihiko Nakao (KEK)

mikihiko.nakao@kek.jp

2022.11.30 Belle II Trigger/DAQ Workshop 2022

# Introduction

### FTSW4

- Next generation FTSW with fully optical inter-rack connections

- Compatible with FTSW3 for short CAT7 connections

- Cost effective solution with low-end FPGA with maximal I/O

### Outline of this talk

- Motivation

- Part selection progress

- Board layout plan

- Use case for CDC FEE upgrade

## **Motivation**

#### Solution to the CAT7 problem

- = Up to  $\sim$ 100mV noise on inter-crate CAT7 cables ( $\leq$ 1m CAT7 is still fine)

- No further improvement is expected, b2tt over fiber would be a solution

#### Upgrade opportunity for the new CDC FEE

- Large number of FEEs (299), unchanged

- JTAG should be faster (now: 41M bits/FEE  $\rightarrow$  new: 91M bits/FEE)

- Opportunity to deliver b2tt to CDC FEEs over fibers, if we have a high-density optical FTSW

- Opportunity to implement a backup route of clock, b2tt, belle2link on multi-port transceivers

#### By-products

- High-density optical FTSW can be directly connected to optical fiber version of PCIe40

- Intermediate FTSW for KLM and ARICH may be removed

- (need a new route to reprogram on-detector TOP FTSW3)

# Part selection (FPGA and VME)

Except for FPGA, devices are chosen from those available in market stock

### FPGA

- No Xilinx FPGA in the stock, need a VERY long delivery time

- Large number of general I/O pin is needed

- Considered: Spartan-7, Artix-7, Artix-Ultrascale+

- $\,$  Artix-7 has the largest number of I/O pins (400 pins), although it is still marginal

- Choice: Artix-7 XC7A200T-1FBG676

- 2 chips from unofficial market place in hand

- 2 from official distributor to be delivered in May 2023

- No secondary FPGA (simpler than FTSW3!)

- Configuration flash memory

- Micron MT25QU128 (or other product)

- CPLD and VME I/O

- > XC95288XL-7TQG144C as a 5V tolerant CPLD for VME interface

- IO-bit DIPSW to set the address

- With just 5 more LVCMOS/TTL chips to form the VME interface

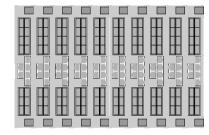

# **FPGA** pin counting

- Artix-7 I/O pins

- $\rightarrow$  400 I/O pins are divided into 8 banks  $\times$  50 pins (up to 24 LVDS pairs)

- LVDS I/O requires 2.5V VCCIO, other I/O requires 3.3V VCCIO

#### LVDS pin counting

- Ourrent design uses 118 LVDS pairs

- $\odot$  In principle, they fit in 5 banks with 2.5V VCCIO, leaving 150 I/O pins with 3.3V VCCIO

- Fully utilizing the pins is quite a challenge

(below is one of my earlier trial, 98 LVDS pairs from 5 banks in 3 layers, not optimized)

| S. |    |    | 5  |   |   |     |     |    |    |     |    | •  |   | ٠          |   | ۰ |   |   | ٠  |    | 140 |   |     |     |          | 0        |

|----|----|----|----|---|---|-----|-----|----|----|-----|----|----|---|------------|---|---|---|---|----|----|-----|---|-----|-----|----------|----------|

| ÷  | S  |    | 5  | õ | ā | ē   |     |    |    |     |    |    |   |            | ۰ | õ | 2 | 8 |    | 6  | 8   | - | (a  | 5   |          |          |

| ٠  | 2  |    |    | 8 |   | le, |     |    |    |     | ۰  |    | • |            |   | ò | ø | a | e  | °o | ۲   |   | c   | 5   | 'n       |          |

| ÷  | 3  |    |    | 6 |   | Ċ.  | e   |    |    |     |    |    |   |            | ۰ | ø | ø | ٠ | ٠  |    | •   | k | ٠   | ٠   | ŝ.       | 0        |

| ٠  | э  |    |    | 0 |   |     | (e  | 0  |    |     |    | •  |   | ٠          | • | ø | ٠ | ٠ | .0 | ٠  |     |   |     | ٥.  | ٠        | •        |

| ø  | Y  |    | b) | ø | 2 | Q2  | ()e | ٥  | 0  |     |    |    |   | .0         | 0 | X | ø | ٠ | ø  | 0  | 0   | 2 | ٠   | e.  | 1        | 80       |

| ٠  | 4  |    |    |   |   |     |     | Ç, |    | ۰   | ۰, | .0 | ø | 36         | 0 | σ | ٠ | ø | •  |    | ۰   |   |     | ٠   |          | 0        |

| ٠  | 3  |    |    | 0 |   |     |     |    | ۰  |     |    |    |   |            | σ | ۲ | ø | С | ø  |    | ۰   |   | ю   |     | o        | •        |

| 0  | 3  |    | 2  | 0 | 2 | 0   | 2   | ္စ | R  | ٠   |    |    | œ | 9          | ø | o |   | ٠ | 0  | 0  | ю   | 0 | •   | ٠   | •        | •        |

| 0  | 3  |    | 2  | 8 | 0 | ς.  | 2   | 0  | ,e | 00  | ø  | 2  | 0 | 8          | σ | σ | ۰ | ø | ø  | 0  |     | e | ς.  | œ   | .0       |          |

| 9  | 2  |    | 9  | 2 | • | æ   | 2   | 0  | 18 |     | ő  | 0  |   | , <b>e</b> | 9 | o | • | • | e  | 0  | .*  | • | 9   | •   | ्        | 0        |

| 9  | 2  | ١. | Þ  | 9 | 9 |     |     | 8  | 0  | ιœ  | Q  | æ  | 0 | •          |   | 0 | 9 | 9 | 9  | .0 | ۰.  | s | 9   |     | <u>.</u> | .•       |

| 9  | 1  |    | 2  | 2 | 8 |     |     |    | 1  |     | 2  | 2  | 0 | 2          | ø |   | 2 | 2 | 2  | 9  |     | 2 | e.  | 2   | æ        |          |

| 2  | 2  | 2  | 2  | 2 | 5 |     |     |    | 9  | 9   | 2  | 9  |   | 2          |   | 2 | 9 |   | 3  |    |     | 2 | 12  | 2   |          | 2-       |

| 2  | 2  |    | 2  | 9 | 2 | ۰.  |     |    | 2  |     | 2  | 8  |   | 2          | 2 | å | 2 | 9 | 2  |    | •   | 2 | 5   | 2   | •        |          |

| 2  | 2  |    | 1  | 2 | 2 | 3   |     |    | 3  |     | 2  | ě  |   | 2          | 2 | 2 | 2 | 2 |    | •  | ୍ଦ  |   | 2.1 |     | •        |          |

| z  | 2  |    | 2  | z | 2 |     |     |    | 2  | m   | 2  | 2  | ŏ | 2          |   | z | 2 | - | 2  |    | •   | 2 | 1   | 1   | 2        | - C      |

| ž  | 2  | 1  | ŝ  | 2 | č |     |     |    | 2  |     | 2  | ě  |   | 2          | ž | ž | ž | 2 | 2  | 2  | 2   | 2 | ٥.  |     | 2        | -        |

| ă  | i  |    | 5  | š | a |     |     |    | ā  |     | ő  | ŏ  |   | 8          | ÷ | ŏ | ä | a | a  | 2  | •   | 2 | 24  | 2   | 1        |          |

|    | 2  |    | 2  | ž | 2 |     |     |    |    | . " | 1  | 1  | - | ő          | 5 | 6 | 1 | 1 | 1  | •  | 2   |   | 2   | 6   | •        | 0        |

| ő  | ŝ  | i. | 5  | ā | ā | 4   | 1   |    | ā  |     |    | •  |   | ä          | m | ä | ā | ñ | -  |    | ്   | 6 | 6   | •   | ۰.       | <b>.</b> |

| õ  | ł  |    | b  | õ | ā | 4   | ē   |    |    |     |    |    |   |            | ö | ē | ē | ē | ÷  | ē  | 10  | 6 |     | ē   | 2        | 0        |

| ó  | 6  | ŝ  | 6  | é |   | ē   |     |    | e  |     | ۰  |    | 0 |            |   | ø |   | ÷ |    |    | 0   |   | 20  | ie. |          | 0        |

| 0  | é  |    | D  | ۰ |   | e   |     |    |    |     |    |    |   |            | ۰ | ۰ | ۰ | ٠ | 8  |    |     |   | 0   | 0   | ٥        | •        |

| ö  | ×. | 5  | ò  | ÷ | â | e.  |     | •  |    | ۰   |    | 0  |   | ۰          |   | ò |   | ٠ | 6  | •  | °o  | 5 | 10  | 6   | •        | 30       |

| ŝ. |   | d  | ł  | ٠ | ł  | 4  |    |     |     |     |    | •  |      |    |   | é. | ÷  | ł  | e. | 4  | i a |          |    |     |     | •   |

|----|---|----|----|---|----|----|----|-----|-----|-----|----|----|------|----|---|----|----|----|----|----|-----|----------|----|-----|-----|-----|

| 5  | 5 |    | 5  | ė | ā  | i. |    |     |     |     |    | -  |      | -  |   | õ  | 2  | 'n | 1  |    |     | 6        |    |     | ۰.  | 1   |

| 2  | 5 |    | K  | 2 | v  |    |    |     |     |     | •  |    | •    |    |   | ā  | æ  | 7  |    |    | 0   |          | 1  | 67  | ۰.  | ٩.  |

| 5  |   |    |    | v | s  | e. |    |     |     |     |    |    |      |    | ۰ | ā  | 2  | 2  | 2  | e  | 2   | ŕ,       | r. | 1   | e   | 1   |

| ÷  |   |    |    |   | s  | 5  | ė  | 10  | . 0 |     |    | •  |      | ۰  | é | è, |    | 1  | 1  | 1  | 6   | 2        | 2  | ۰.  | 2   | ۰.  |

| õ  |   |    |    | 8 |    |    |    |     |     |     |    |    |      | ō  | ō | 2  | 6  | •  | 6  | e. | °e  | e.       | 6  | ι.  | 6   | ie. |

| ٠  |   |    |    |   |    |    |    | Ŷ   |     | e.  | .0 | ۰, | ø    | 26 | 0 |    |    | 'n | Ĉ. | Ĉ. |     | ٥.       | ĉα | ĉ.  | ٥.  | i.  |

| ė, |   | ê  | i, | • | 'e |    |    | Ŷ   | Ç0  |     |    |    |      |    |   | o  |    | è  | Ċ0 | Če | ĉ   | e.       | ¢. | c   | (o  | •   |

| •  | e | ð  | ń  | 0 | ÷. | 0ê | Ű. | 0   | ñx. | ÷   |    |    | ď    | ø  | ø | 0  | 20 | ٠  | ¢. | Čē | 6   | Č¢,      | 6  |     | Ċø. | ie. |

| ø  | 6 |    | 5  | 8 | 0  | e. | 0  | Ç,  | ø   | 0   | ø  | 2  | 0    | 8  | 0 |    | Ö  | e  | (4 |    | 64  | 6        | С  | (a  | ٠   |     |

| 8  | 4 |    | þ  | ۰ | ٠  | (e | Č. | ) e | ů8  | ٠   | ø  | ò  | ĨQ.  | 0  | 0 | o  | ٠  | 0  | (e | (e | Č4  | 8        | 6  | ંગ  | (o  | ိုစ |

| 0  |   | Õ  | D) | ۰ | •  | 0  | Č. | 18  | 0   | 0   | ۲  | ۲  | 0    | 0  | 0 | 0  | ۰  | 8  | (e | ĩ. | č.  | Ç,       | (e | ۰   | 6   |     |

| 0  | 4 | 0  | 0  | ٠ | 8  | 0  | 6  | • • | 18  |     | ø  | œ  | 0    | ٠  | Ø | 0  |    | 0  | e. | (6 | 0   | 0        | ς. | 60  | 68  | •   |

| ٠  | Q | 1  | •  | ٠ | •  | 4  | •  | •   | 0   | 00  | ø  | æ  |      | ٠  | 0 | ۰  | 0  | ۰  | 6  | 0  | ¢.  | 6        | 6  | 0   | œ   |     |

| ۰  | 4 | 1  |    | 0 |    |    |    | • • | 18  | . 0 | .0 | æ  |      | ٠  |   | .0 | ۰  | 0  | 18 | ς. | 0   | х.       | с. | (0  | 0   |     |

| ۰  |   | 1  | P  | ۰ | •  | 8  | 1  | •   | 0   | .0  |    | ŝ  | ۰    | ٠  | ٠ | ۲  | ۰  | 9  | 0  | ς. | ÇC, | Ç.       | Ç. | ۰   | ွစ  | 8   |

| •  |   |    | 8  | 0 | 9  |    |    | • • | . 8 |     | æ  | 0  | 0    | ٠  | ٠ | ۰  | 0  | 9  | х. | κ. | ς.  | ь.       | 18 | 6   | ۰,  | .•  |

| •  | 2 | 1  | 2  |   | 9  | •  | 9  |     |     | 0   |    | 2  | .0   | 2  |   | ۰  | 2  | 2  | κ. | 2  | ς.  | х.       | ς. | ٠   | 6   | 2   |

| 9  | • |    | 2  | • | 2  |    | 0  | 2   |     |     | œ  | 9  | - 99 | ٠  | 2 |    | œ  | 5  | ۶. | ν. | ο.  | <u>و</u> | ۶. | ч.  | 6.  | 2   |

| 2  | 2 | 1  | 2  | Ŷ | 2  | 1  | 1  |     | 2   | ۰   | ۰  | •  | •    | 2  | 2 | 2  | 2  | 2  | 1  | 8  | ۰.  | 6        | 5  | 2   | 6   | 2   |

| ÷. | 2 | Ľ. | 2  |   | 2  |    | 2  | ÷   | 9   |     |    | •  |      | 2  | 2 | 0  | 2  | 2  | 2  | ۵. | 0   | έ.       | 2  | 5   | ٥.  | .9  |

| 2  | 2 | ł  | 2  | 2 | 2  |    | 2  |     |     |     |    |    |      | ۴  | 2 | 2  | 2  | 2  | ē. | ē. | ē.  | ð        | 13 |     | ь.  | 2   |

| 2  | 2 |    | 2  | 2 | ~  |    |    | ۰.  |     |     |    |    |      |    | * | 2  | 2  | 2  | 2  | 5  | 6   | 6,       | 5. | 5-  | 1   | 6   |

| 2  | 2 |    | 2  |   | 2  | 12 |    |     |     |     | •  |    |      |    | - | 2  | 2  | 2  | 8. | ٥. | 0   | 6        | 52 | 22  | ۰.  | 12  |

| 2  | 2 |    |    |   | 2  | 12 |    |     |     |     |    | ~  |      |    | ٣ |    | 2  | 2  | 3  | 6  | ۰.  | ō.       | 2  |     | ٥.  |     |

|    |   |    |    | • | ٠  | ٠  |    | e   |     | ٠   |    | •  |      |    |   |    |    | -  |    |    |     |          |    | ••• |     |     |

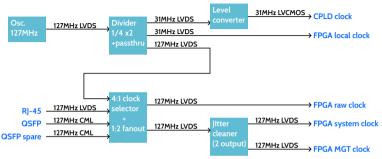

# Part selection (clocking)

- Oscillator: KDK KEM35AT-L 127.216MHz

- Divider+passthru: SY89873L

- Level converter: DS90LT012ATMF

- Selector (4:1) + fanout (1:2): SY89547LMG

- Jitter cleaner: CDCE62002

3.3V device only

**6** /12

## Part selection (power)

#### 3.3V from 5V of VME

- Originally considering a DC-DC converter with multi-voltage output

- Changing the design: use 3.3V only device other than FPGA

- Confine the other voltages only near the FPGA

- Large-current 3.3V DC-DC suggested by Dima: LMZ10505

- External 3.3V

- Option to use JO connector of KEK-VME, and from a on-board terminal (same as FTSW3)

- **2.5V, 1.8V, 1.2V, 1.0V**

- Only for Artix-7, use reliable LDO regulators (same as or similar to FTSW3)

- 2.5V (VCCIO for LVDS): LT1963

- 1.8V (VCCAUX): LT1963 or LT1761

- 1.2V (MGTAVTT): LT1963

- 1.0V (VCCINT, MGTAVCC): TPS74401

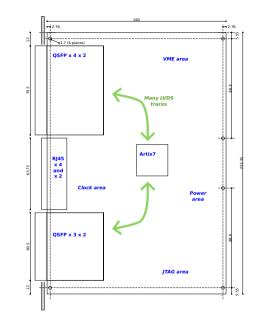

# Part selection (connector)

No optional daughter card (no FMC)

### QSFP

- Current trend is into high-end O(100Gbps) transmission

- OSFP is probably the only available low-end multi-port transceiver

- 2 QSFP cages can be mounted by a belly-to-belly configuration (to maximize the front panel area usage)

- PC board has to be a bit thicker ( $\geq$  2.2mm, like FTOP, while standard is 1.6mm)

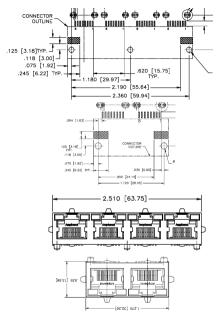

### **RJ-45**

- Several RJ-45 ports are needed

- Priority in maximizing the number of optical ports

- No RJ-45 connector designed for belly-to-belly (only double-story RJ-45 connectors like FTSW3)

- A solution found: 4-port RJ-45 and 2-port RJ-45 in belly-to-belly

- Maximizing the number of ports

- 14 QSFP cages + 6 RJ-45 connectors

- About the limit of the number of pins of Artix-7

FTSW4 development status M. Nakao

**9** /12

### **FTSW4 crates for CDC**

### FTSW4 counting

- Minimum 19 FTSW4 modules to cover 300 CDC FEEs (7×3=21 FTSW4 modules is more logical configuration)

1 more FTSW4 in the main TTD crate to deliver signals

1 more FTSW3 to deliver JTAG signals to FTSW4

1 VME CPU for JTAG

- Fully packed 2 VME 6U crates,

or more logical 3 VME 6U crate configuration

#### FTSW4 location

- FTSW4 can be located in E-hut (no length limitation of CAT7)

- FTSW4 on the detector will save the fiber cost, but less accessible

- One rack space for FTSW4 crates, and one rack space for patch panels

- MPO fiber (clock, b2tt, JTAG, b2link) directly from E-hut to FEE? (cabling would be a lot simpler)

# **Quantity and Cost**

#### Number of boards

- 20-22 FTSW4 for CDC

- 1+1 FTSW4 for KLM+ARICH in E-hut to reduce 9 intermediate FTSW3 (no real gain for the current FEEs of other subdetectors)

- $\,$  Produce 30 boards if no other FEE upgrade which adopts optical b2tt/jtag

- Cost estimate

- $\,$  FPGA  $\sim$  500 USD per module

- $\sim$  Connectors  $\sim$  300 USD / module

- Oscillator  $\rightarrow$  need to purchase a reel for CDC (8000 USD total)

- $\,$  Power chips  $\sim$  100 USD / module

- $\,$  Clock chips  $\sim$  50 USD / module

- Passive parts and extra parts for JTAG to be estimated

- $\sim$  QSFP modules  $\sim$  1,000 USD / module

- $\triangleright$  Front panel  $\sim$  50 USD / module

- $\sim$  PC board and assembly  $\sim$  500 USD per board

- Total:  $\sim$  2,500 USD per board, 75,000 USD total (?)

- (MPO fibers and CDC patch panel are not included)

## Plan

FPGA pin counting needs a bit more work

- Priority since it may affects the part selection

- Need to allocate time to concentrate

#### Start buying parts

- Clock related parts may disappear from market stock

- Not much budget of this FYL left

#### JTAG needs more work

- JTAG-over-b2tt should be avoided for new CDC FEE

- JTAG-over-optjtag to be driven by FTSW4, but need more thinking

#### More work on details

- Ethernet option (both optical and RJ-45)

- Passive components, especially on noise mitigation

### Schematics

Maybe towards the end of the FY or beginning of next FY