# ARICH requirement for high rate/triggerless DAQ

### Kenta Uno Niigata university

### Belle II Trigger/DAQ Workshop 2022 02.Dec.2022

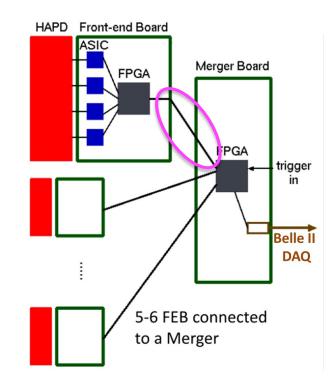

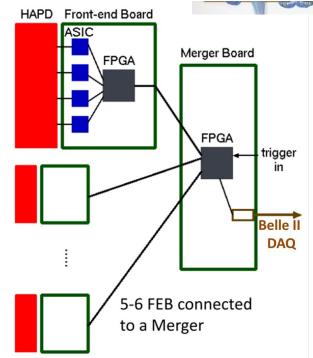

# Limitation of trigger rate ARICH FEB

- Sends data to merger using 4 lines with 63.6 MHz clock.

- Event size: 4 bit/ch \* 144ch + 80 (header) = 656 bit.

- $\rightarrow$  164 clocks to send one event.

### **FEB** condition

- Issue maximum 10 triggers within 26.4 us.

- ARICH fully relies on this condition

- → Overflow never happens

- →  $f = 1.0/(26.4/10) \sim 380$  kHz is the limit

- **X** Difficult to remove this condition

- A lot of modification (firmware) is needed

- $\rightarrow$  Triggerless readout is not possible

HAPD : 144 ch

# **Event size**

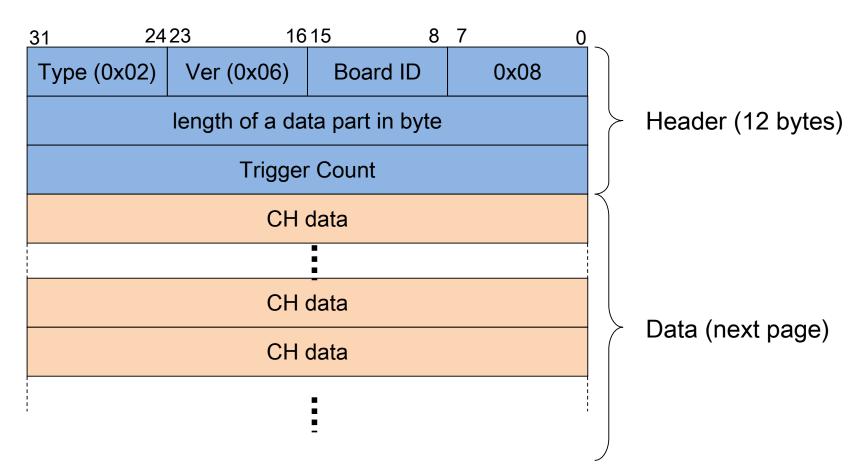

<u>Header</u>

#### **\***ARICH: 420 FEB, 72 Merger Board

- 12 bytes merger header per merger

- 22 bytes FEB header per FEB

- Belle2Link header: 36 bytes per Belle2Link.

Data per FEB

- Raw mode: 4 \* 144 bit = 72 bytes FEB data

- Suppressed mode: 2C bytes (C: #channels with hit)

### Event Size:

- Raw mode: 12 \* 72 + 36 \* 72 + (22 + 72) \* 420 ~ 43 kB

- Suppressed mode: 12 \* 72 + 36 \* 72 + (22 + C) \* 420 ~ (13+0.4C) kB

- C: average #hits per HAPD. Typically, C < 1 → <15 kB</li>

Large part of the data is header

This is necessary to check the consistency of the FEB data  $\rightarrow$  No plan to change the format.

3

# Limit/Improvement of FEE

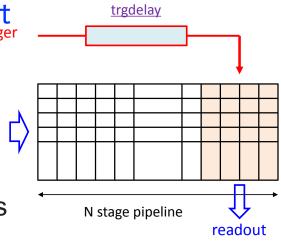

- Internal logic of the FPGA for the hitdata readout

- System clock is 63.6 MHz (1 clock = 15.7 ns)

- Data inside pipeline is shifted every hdcycle clocks

Bipeline has N stage, where N = 56

- Pipeline has N stage, where N = 56

- Trigger signal is delayed by trigdelay \* hdcycle clocks

- Last 4 stages of the pipeline are read out

- $\rightarrow$  Hit data is kept for ~(N 2 trgdelay) \* hdcycle \* 15.7 ns

Current FEE (N = 56, hdcycle = 8, trigdelay = 16)  $\rightarrow$  Keep data for  $\sim 5.0$  us

### Consideration

- Increase the depth, N (Already confirmed firmware with N=116 works)

- 10 us latency is possible

- Option to reduce time window to be more tolerant to beam bkg

→ If we adopt 10 us, it's difficult to adopt this option 4

Backup

Nishida-san's slide

## **ARICH Data Format**

Data format from one Merger Board (= one Belle2Link).

Nishida-san's slide

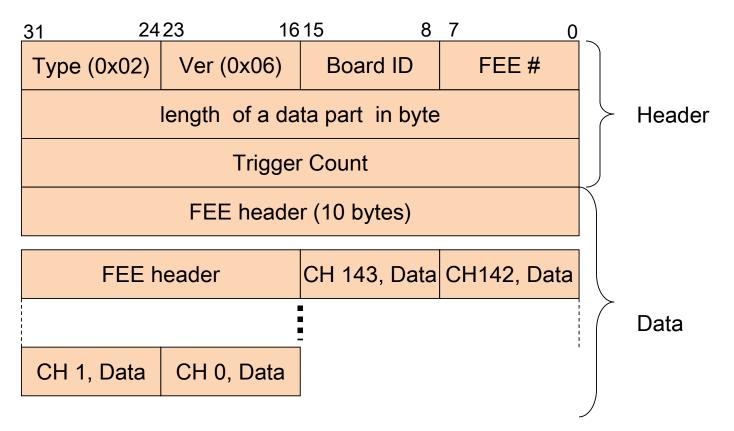

## **ARICH Data Format**

CH Data in Raw Mode

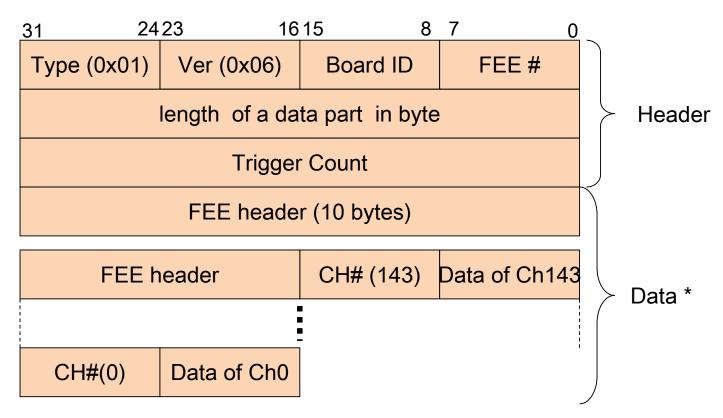

### Nishida-san's slide ARICH Data Format

#### CH Data in Suppressed Mode

\* If a ch has no hit data (Zero), its data is not transmitted.

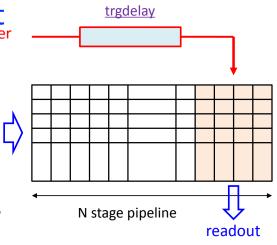

# Limit/Improvement of FEE

- Internal logic of the FPGA for the hitdata readout

- System clock is 63.6 MHz (1 clock = 15.7 ns)

- Data inside pipeline is shifted every hdcycle clocks

Bipeline has N stage, where N = 56

- Pipeline has N stage, where N = 56

- Trigger signal is delayed by trigdelay \* hdcycle clocks

- Last 4 stages of the pipeline are read out

- $\rightarrow$  Hit data is kept for ~(N 2 trgdelay) \* hdcycle \* 15.7 ns

Current FEE (N = 56, hdcycle = 8, trigdelay = 16)  $\rightarrow$  Keep data for  $\sim 5.0$  us

#### Plan

- Increase the depth, N (Already confirmed firmware with N=116 works)

- Shorter time window (hdcycle) depending on beam background

- $\rightarrow$  10 us latency is possible by updating firmware