### **TOPTRG Status**

Tianping Gu, Erfei Wang, Vladimir Savinov

University of Pittsburgh

Oct. 5<sup>th</sup>, 2021

### **TOP TRG Status Since Last B2GM**

As reported at previous B2GM, standalone TOP-based triggering does not seem to be possible due to excessively high beam-related background.

To understand how to make TOP TRG work in presence of such background we have been investigating using correlations of TOP TRG info with CDC 2D TRG tracks.

#### Since last B2GM, we:

- Performed offline simulation for several slot-level and combined timing algorithms using trigger readout data.

- Investigated the TOP TRG efficiency for hadronic events of relatively high charged particle multiplicity.

- (Tentatively) agreed on the CDC-TOP matching algorithm.

- Agreed to stream all TOPTRG slot decisions to GRL and perform matching at GRL.

- Started to port TOPTRG FW to UT4, core logic ported successfully.

- Tested the data link between UT4 and TOPFEE.

- Confirm the TOPTRG core logic work on UT4.

Collision data exp/run 26/766:

Red: TOP main readout hits

Blue: TOP TRG waveform readout timestamps

Currently, TOP TRG makes its timing decisions completely independently of ECL and CDC.

Therefore, in contrast to TOP main readout, TOP TRG is unable to reject background timestamps using digitization window w.r.t. the actual L1 decision.

We choose a narrow clock cycle window (e.g., between 100 and 200 clock cycles) to exclude slot-level background-based timing decisions.

This is an approximation for CDC-TOP TRG-level matching, grlcdc bits could be set to "high" for 200 clock cycles when there is a track pointing at a slot.

### **CDC-TOP** matching

Performed offline simulation for several slot-level and combined algorithms:

- 1.

Slot-level: maximum loglikelihood in the fixed timing range [100,200]. (logL threshold cut) Combined: average of slot-level decisions with CDC 2D TRG track matching.

To be sent to GDL: this combined decision.

- 2. Slot-level: maximum loglikelihood in the fixed timing range [100,200]. (logL threshold cut) Combined: slot-level decision with the most hits with CDC 2D TRG track matching. To be sent to GDL: this combined decision.

- 3. Slot-level: generate slot-level decision on every clock cycle. (logL threshold cut) Combined: average of slot-level decisions for the same clock cycle with CDC 2D TRG track matching. To be sent to GDL: combined decision with the largest number of slot-level decisions.

- 4.

Slot-level: generate slot-level decision on every clock cycle. (logL threshold cut)

Combined: slot-level decision with the most hits of the same clock cycle with CDC tracks matching.

To be sent to GDL: combined decision with the largest number of slot-level decisions.

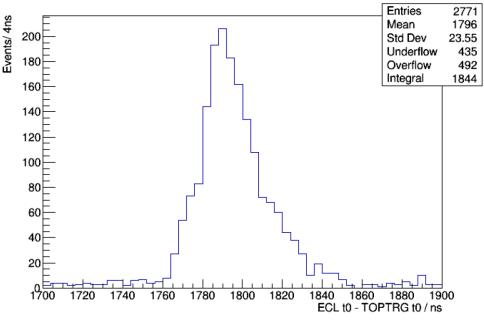

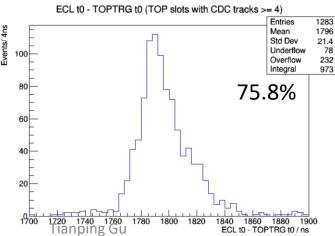

### Approach 2: exp26 run 766, hadronic events

Collision exp26 run 766, hadronic events

Loglikelihood threshold: 10000000 (equivalent to ~15 timestamps)

Physics region (waveform readout clock cycles): [100, 200]

TOP TRG trigger waveform used in simulation

TOP-CDC matching is required for slots included in the algorithm

Figure of merit: TOP TRG timing w.r.t. ECL timing

#### Approach 2:

Slot-level timing decisions: maximum loglikelihood in the fixed timing range [100,200]. (logL threshold cut)

Combined timing decision: slot-level decision with the most timestamps with CDC 2D TRG track matching.

Use the slot t0 with most hits instead of average of all slot t0s => suppress background

Efficiency: 1844/2771 = 66.5% RMS: ~ 24 ns, Resolution: ~ 15 ns Resolution improves significantly

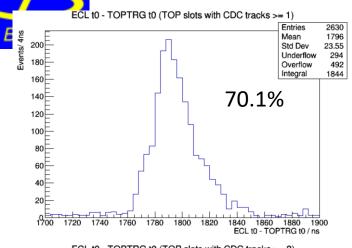

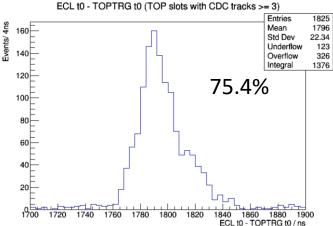

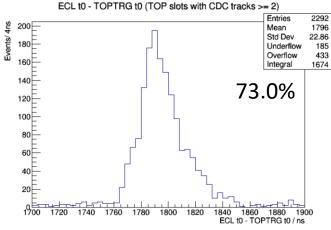

### Approach 2: exp26 run 766, hadronic events with high particle multiplicity

- Loglikelihood threshold: 10000000 ~15 hits

- Physics region: [100, 200]

TOP TRG to distributions for events which have more than n TOP slots with CDC tracks pointing to.

Efficiency for high-multiplicity hadronic events ~75%

RMS: ~ 22 ns

Resolution: ~ 13 ns

# **Summary of CDC-TOP matching studies**

- Offline simulation performed for several slot-level and combined algorithms.

- Currently, the best results obtained using approach 2 (using timing from the slot with the largest number of timestamps):

Efficiency for hadronic events: ~67% Efficiency for high-multiplicity hadronic events: ~75% (ECL-TOP) timing resolution for hadronic events: ~15 ns (ECL-TOP) timing resolution for high-multiplicity hadronic events: ~13 ns

#### Discussion:

- Agreed to use approach 2 as tentative CDC-TOP matching algorithm.

- Agreed to stream all TOPTRG slot decisions to GRL and perform matching at GRL.

- Proposed TOPTRG -> GRL data format, send slot-level info to GRL (T0, hit number, flag).

### TOPTRG->GRL data format

| Flags for slot-t0:      |

|-------------------------|

| 1hit * 16slots = 16hits |

Number of hits: range [0,255] 8bits \* 16slots = 128bits

Slot-t0: range [0,46080] / 2ns 16bits \* 16slots = 256bits MSB 11 bits are common for all slots (reject slot-t0 outside 32\*2=64ns window), 11bits + 5bits \* 16slots = 91bits

However, MSB 11 bits should be sent from both UT3s for validation.

Total: 16+128+91(+11) = 235(246)bits

GTH 8 lanes from TOPTRG to GRL:

5Gbps: 256bits/127MHz

| bit                                                  | 0                                     | 1 | 2 | 3            | 4                       | 5 | 6 | 7 |  |

|------------------------------------------------------|---------------------------------------|---|---|--------------|-------------------------|---|---|---|--|

| [0:7]                                                |                                       |   |   | Flag         | lot 1-8                 |   |   |   |  |

| [8:15]                                               | Hit numbers slot 1 Hit numbers slot 2 |   |   |              |                         |   |   |   |  |

| [16:23]                                              |                                       |   |   | Hit num      | bers slot               | 2 |   |   |  |

| [24:31]                                              | Hit numbers slot 2 Hit numbers slot 3 |   |   |              |                         |   |   |   |  |

| [32:39]                                              |                                       |   |   | Hit num      | bers slot               | 4 |   |   |  |

| [40:47]                                              |                                       |   |   | Hit num      | bers slot               | 5 |   |   |  |

| [48:55]                                              |                                       |   |   | Hit num      | bers slot               | 6 |   |   |  |

| [56:63]                                              |                                       |   |   | Hit num      | bers slot               | 7 |   |   |  |

|                                                      |                                       |   |   |              |                         |   |   |   |  |

| bit                                                  | 0                                     | 1 | 2 | 3            | 4                       | 5 | 6 | 7 |  |

| bit [64:71]                                          | 0                                     | 1 | 2 | 3<br>Hit num |                         |   | 6 | 7 |  |

|                                                      | 0                                     | 1 |   |              | bers slot               | 8 | 6 | 7 |  |

| [64:71]                                              | 0                                     | 1 |   | Hit num      | bers slot<br>ts of slot | 8 | 6 | 7 |  |

| [64:71]<br>[72:79]                                   | 0                                     | 1 |   | Hit num      | bers slot<br>ts of slot | 8 | 6 | 7 |  |

| [64:71]<br>[72:79]<br>[80:87]                        | 0                                     | 1 |   | Hit num      | bers slot<br>ts of slot | 8 | 6 | 7 |  |

| [64:71]<br>[72:79]<br>[80:87]<br>[88:95]             | 0                                     | 1 |   | Hit num      | bers slot<br>ts of slot | 8 | 6 | 7 |  |

| [64:71]<br>[72:79]<br>[80:87]<br>[88:95]<br>[96:103] | 0                                     | 1 |   | Hit num      | bers slot<br>ts of slot | 8 | 6 | 7 |  |

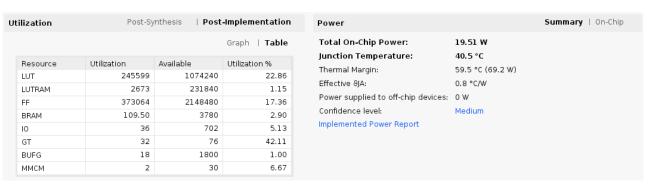

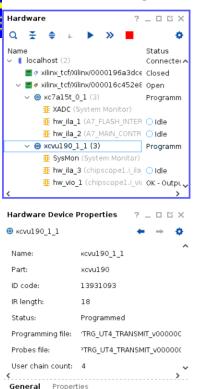

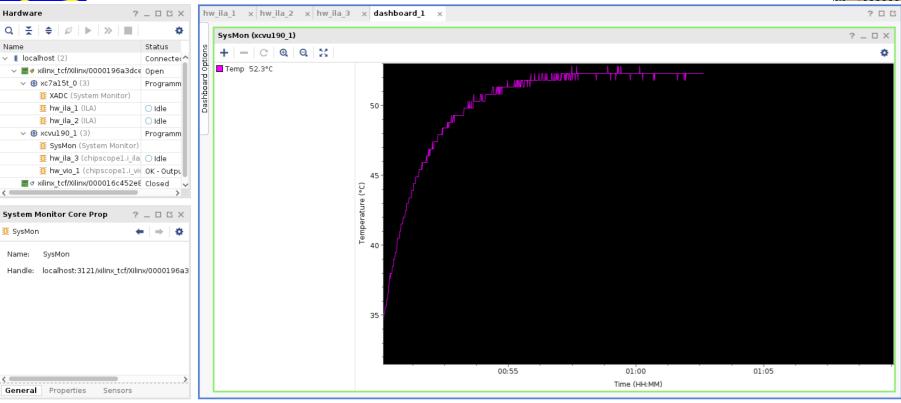

### **Porting TOPTRG to UT4**

32 Aurora 8b10b (GTY transceiver) data links between TOPFEE and TOPTRG.

Tianping Gu

Core logic for slot decision making.

Successfully test on UT4 at KEK using test generator / pulser.

Unno-san and Koga-san adjusted the VME crate and the location of UT4. Now both UT4s are good, stabilize at ~50 °C

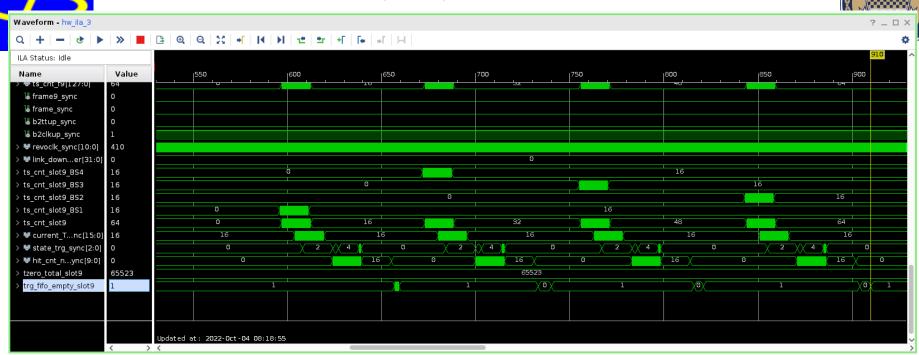

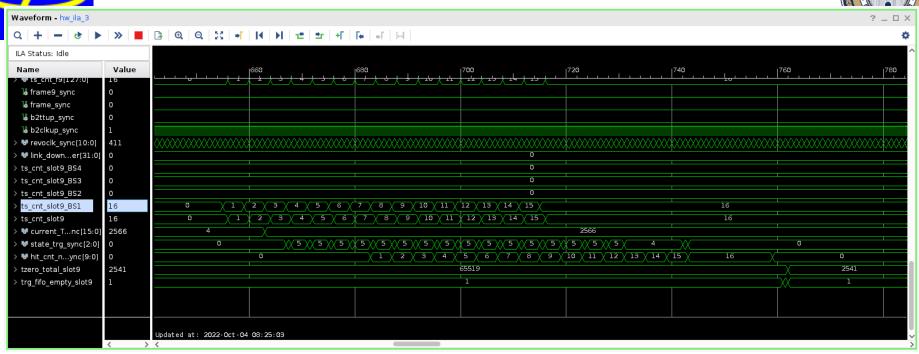

## TOPFEE -> TOPTRG data link (slot 9)

| Naveform by ile 3      |                 |               |                    |                                                   |                                         |            |       |           |             |              |            |       |        |       | _ [       |

|------------------------|-----------------|---------------|--------------------|---------------------------------------------------|-----------------------------------------|------------|-------|-----------|-------------|--------------|------------|-------|--------|-------|-----------|

| Vaveform - hw_ila_3    |                 |               |                    |                                                   |                                         |            |       |           |             |              |            |       |        | ? .   | _ L       |

| Q + - b                | <b>&gt;&gt;</b> | <u> </u>      | ⊠   <b>•</b> F   K | H ± ±                                             | +[ [+                                   | <b>,</b> [ |       |           |             |              |            |       |        |       |           |

| ILA Status: Idle       |                 |               |                    |                                                   |                                         |            |       |           |             |              |            |       |        |       |           |

| Name                   | Value           | 1,400         | 1,405              | 1,410                                             | 1,415                                   | 1,420      | 1,425 | 1,430     | 1,435       | 1,440        | 1,445      | 1,450 | 1, 455 | 1,460 |           |

|                        | 16              | <del></del>   | <del>⋖</del>       | <del>, ~                                   </del> | <del>   </del>                          |            |       |           |             | <del></del>  |            |       |        |       |           |

| frame9_sync            | 0               |               |                    |                                                   |                                         |            |       |           |             |              |            |       |        |       |           |

|                        | 0               |               |                    |                                                   |                                         |            |       |           |             |              |            |       |        |       |           |

| · · · · ·              | 0               |               |                    |                                                   |                                         |            |       |           |             |              |            |       |        |       |           |

| ¼ b2clkup_sync         | 1               |               |                    |                                                   |                                         |            |       |           |             |              |            |       |        |       |           |

| > ₩ revoclk_sync[10:0] | 965             |               |                    |                                                   | *************************************** |            |       |           |             | ************ |            |       |        |       | $\propto$ |

| Iink_downer[31:0]      | 0               |               |                    |                                                   |                                         |            |       | 0         |             |              |            |       |        |       |           |

| ts_cnt_slot9_BS4       | 0               |               |                    |                                                   |                                         |            |       | 0         |             |              |            |       |        |       |           |

| ts_cnt_slot9_BS3       | 0               |               |                    |                                                   |                                         |            |       | 0         |             |              |            |       |        |       |           |

| ts_cnt_slot9_BS2       | 0               |               |                    |                                                   |                                         |            |       | 0         |             |              |            |       |        |       |           |

| ts_cnt_slot9_BS1       | 16              | 0 \1\2\3      | 3 4 5 6 7 8        |                                                   | *************************************** |            |       |           |             | 16           |            |       |        |       |           |

| ts_cnt_slot9           | 16              | 0 \(1\)       | 2 3 4 5 6 7        |                                                   |                                         |            |       |           |             | 16           |            |       |        |       |           |

| ▼ current_Tnc[15:0]    | 16              |               | 16                 | 1/2/3/4/5                                         | <u>/6</u> \7\8\9\                       |            | X     |           |             |              | 16         |       |        |       |           |

| ₩ state_trg_sync[2:0]  | 0               |               | 0                  | Х                                                 |                                         | 2          |       | 5 /       | 4           | Xε           | ž <b>X</b> |       | 0      |       |           |

| ₩ hit_cnt_nync[9:0]    | 0               |               |                    |                                                   | 0                                       |            |       | 1/2/3/4/5 | 6 7 8 9 7 . |              | X          | 16    |        | X     | 0         |

| tzero_total_slot9      | 65523           |               |                    |                                                   |                                         |            |       | 65523     |             |              |            |       |        |       |           |

| trg_fifo_empty_slot9   | 1               |               |                    |                                                   |                                         |            |       | 1         |             |              |            |       |        | Х     | 0         |

|                        |                 |               |                    |                                                   |                                         |            |       |           |             |              |            |       |        |       |           |

|                        |                 |               |                    |                                                   |                                         |            |       |           |             |              |            |       |        |       |           |

|                        |                 |               |                    |                                                   |                                         |            |       |           |             |              |            |       |        |       |           |

|                        |                 | Undated at: 1 | 2022-Oct-04 08:    | 09:11                                             |                                         |            |       |           |             |              |            |       |        |       |           |

|                        | <b>(</b> )      | <             |                    |                                                   |                                         |            |       |           |             |              |            |       |        |       |           |

SCROD test generator: s09a generates 16 timestamps.

TOPTRG receive 16 timestamps and generate the t0 decisions correctly.

# TOPFEE -> TOPTRG data link (slot 9)

SCROD test generator: each boardstack generates 16 timestamps.

TOPTRG receive 4 bunches of timestamps and generate the t0 decisions respectively.

Carrier test generator: s09a carrier 0 generates 16 timestamps.

# Summary

- Performed offline simulation for several slot-level and combined timing algorithms using trigger readout data.

- Investigated the TOP TRG efficiency for hadronic events of relatively high charged particle multiplicity.

- (Tentatively) agreed on the CDC-TOP matching algorithm.

- Agreed to stream all TOPTRG slot decisions to GRL and perform matching at GRL.

- Started to port TOPTRG FW to UT4, core logic ported successfully.

- Tested the data link between UT4 and TOPFEE.

- Confirm the TOPTRG core logic work on UT4.

- Next steps:

- Set up the link between TOPTRG and GRL with new TOPTRG->GRL data format

- Work on implementing CDC-TOP matching logic on GRL

- Set up other necessary part e.g. VME, TOPTRG->GDL, etc.