Systèmes de Référence Temps-Espace

# WhiteRabbit Time dissemination

B2GM FEB-13-2023 D.Charlet, C.Viou, PE.Pottie

# Outline

- WhiteRabbit overview

- IDROGEN board

- Research & Technology project : TIMED

- T+R'EFIMEVE infrastruture

- PCIe400

PAON IV detector

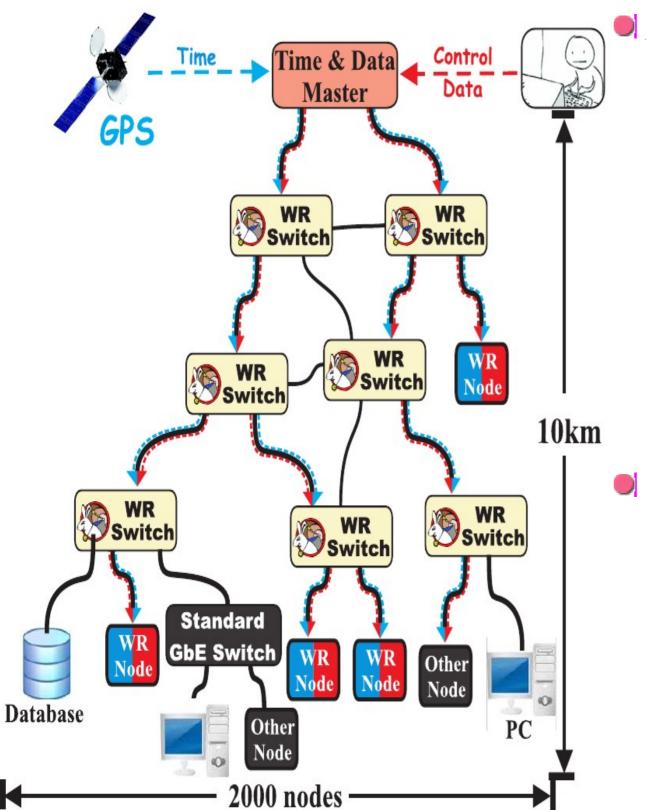

- An extension of Ethernet which provides :

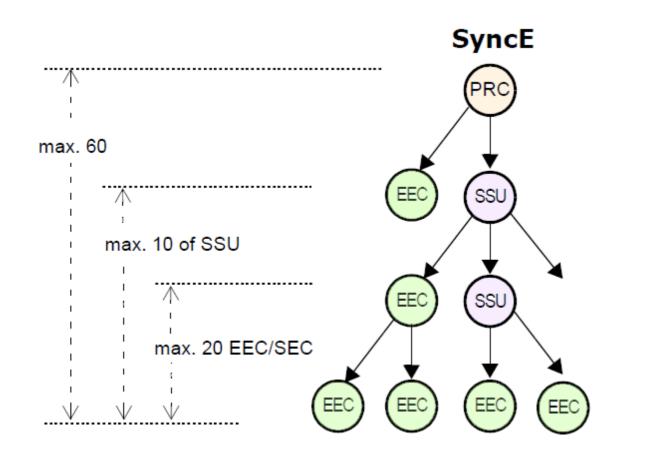

- Synchronous mode (Syn-E) common clock for physical layer in entire network, allowing for precise time and frequency transfer

- Deterministic routing latency a guarantee that packet transmission delay between two stations will never exceed a certain boundary.

- Technology overview

- Precision Time Protocole (IEEE1588)

- Synchronous Ethernet

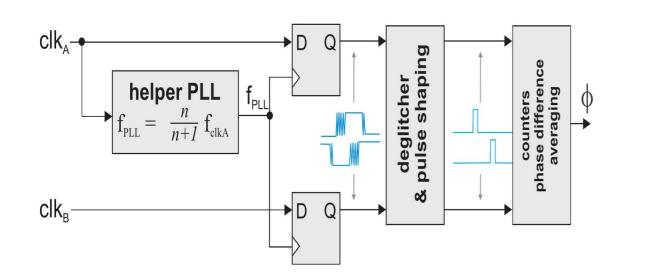

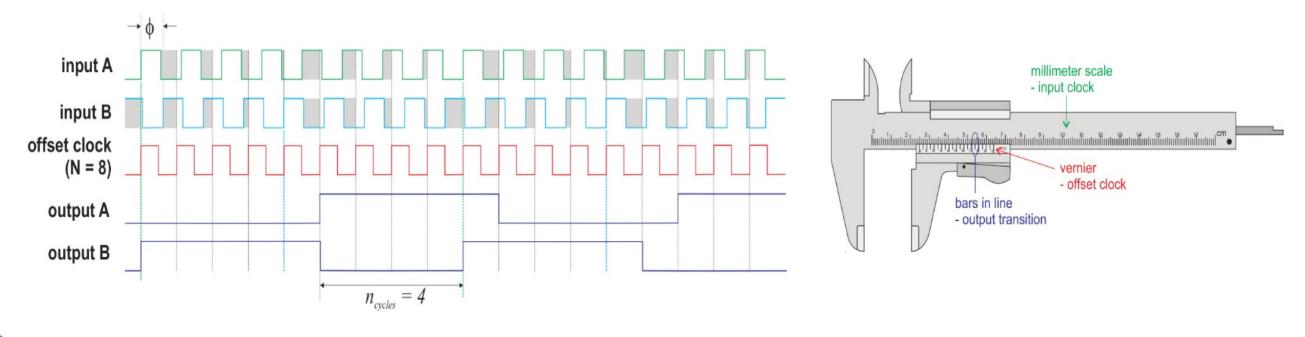

- DDMTD Phase tracking (Digital Dual Mixer Domain) ...

de Nançay

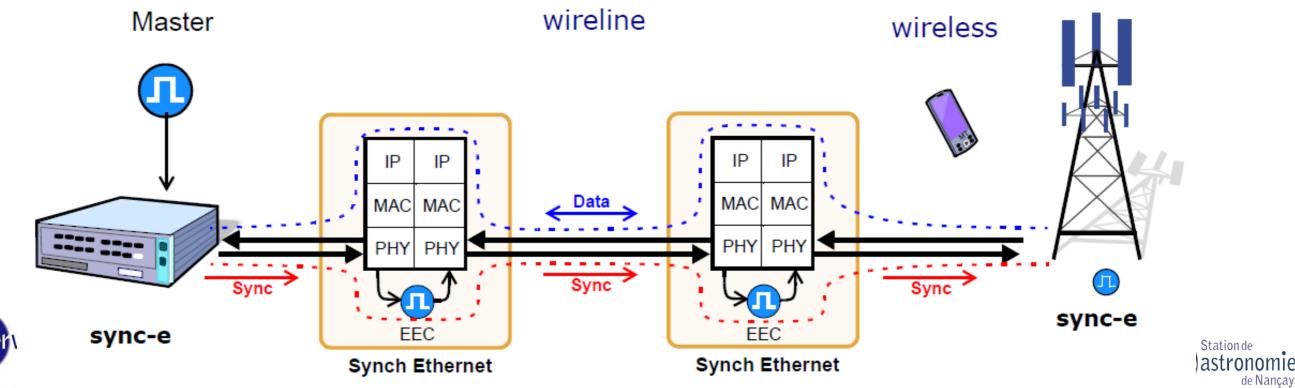

- All network nodes use the same physical layer clock,

- Clock is encode in the Ethernet carrier and recovered by the receiver chip(PHY)

- A master and unique clock for the whole network

- Synchronous digital hierarchy

- High precision clock definition, 20 better than standard Ethernet clock

# Precision Time Protocol (IEEE1588)

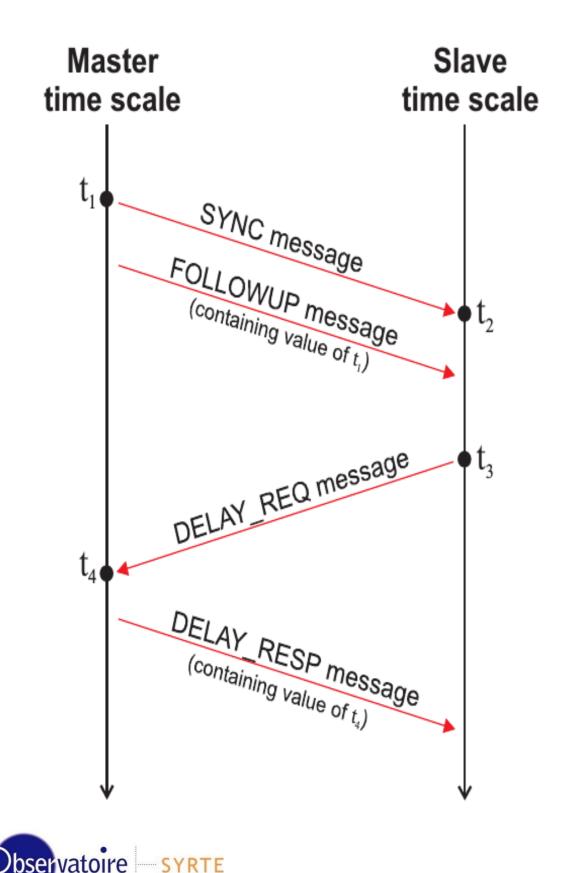

- Packet-based synchronization protocol

- Synchronizes local clock with the master clock by measuring and compensating the delay introduced by the link.

- Link delay evaluated by measuring and exchanging packets tx/rx timestamps

- PTP is used only for compensation of the clock offset

Having values of t1 ...t4 , slave can:

• calculate one-way link delay:

$\delta ms = ((t4 - t1) - (t3 - t2))/2$

- syntonize its clock rate with the master by tracking the value of t2 - t1

- compute clock offset:

offset = t2 t1 + δms

- Measure the phase shift between transmit and receive clock on

- the master side, taking the advantage of Synchronous Ethernet.

- Monitor phase of bounced-back clock continuously.

- Phase-locked loop in the slave follows the phase changes measured by the master.

Systèmes de Référence Temps-Espace

SYRTE

bservatoire

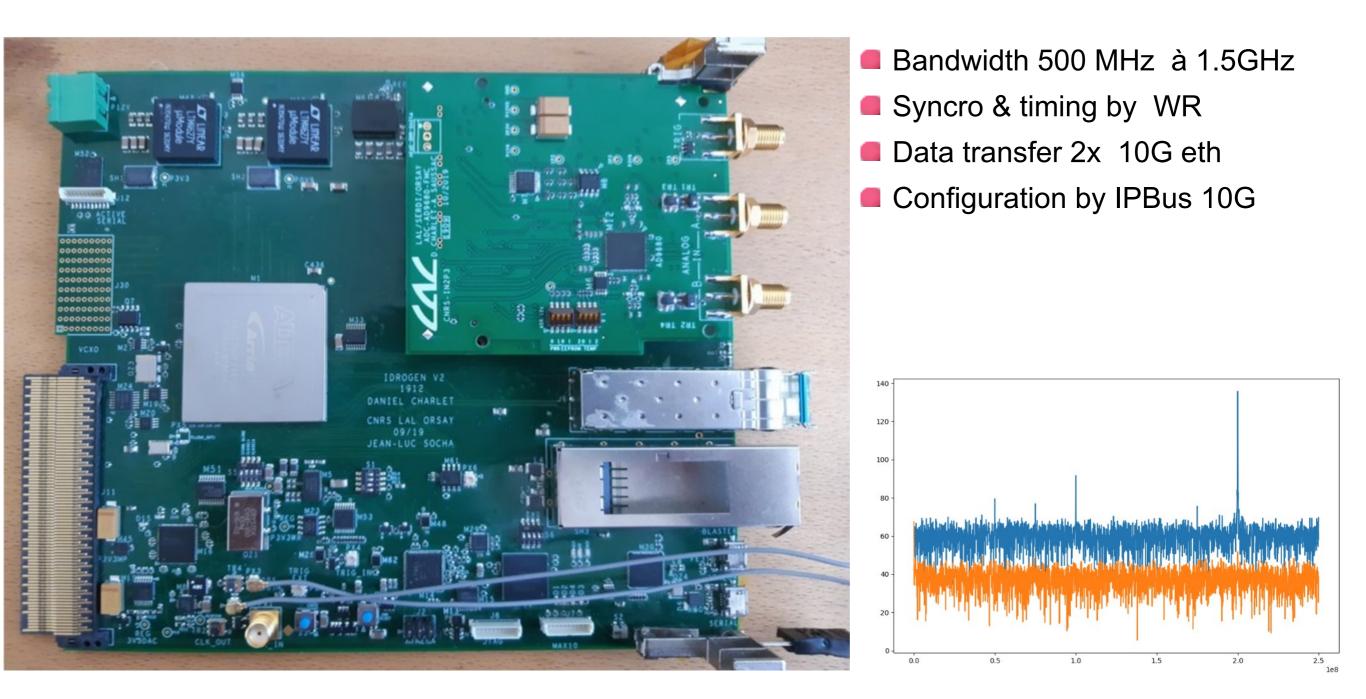

# IDROGEN board

# Low phase noise WR -PTP : IDROGEN

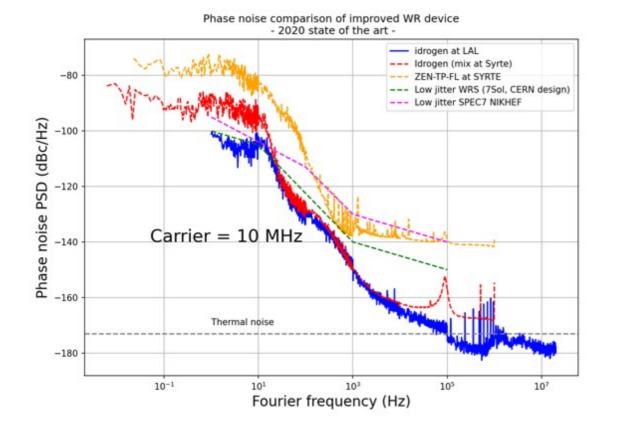

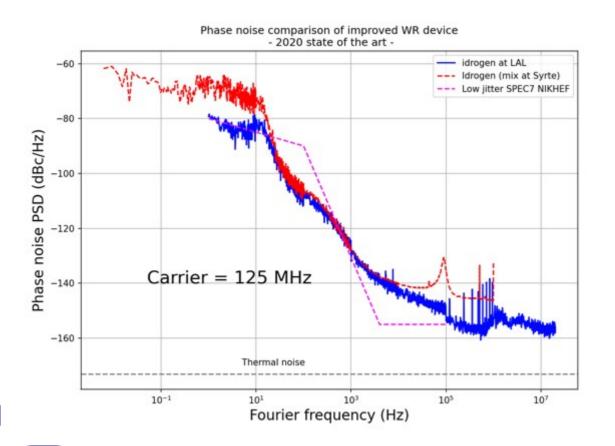

- High performance WR low jitter

- Expertise from SYRTE for clock & qualification

- Design & realization by IJCLAB

- Firmware by Nancay Observatory

- Measures at SYRTE and IJCLAB

http://www.ohwr.org/projects/white-rabbit/wiki/WRReferenceDesign

### **IDROGEN** main features

http://www.ohwr.org/projects/white-rabbit/wiki/WRReferenceDesign

SYRTE

**D**bservatorre

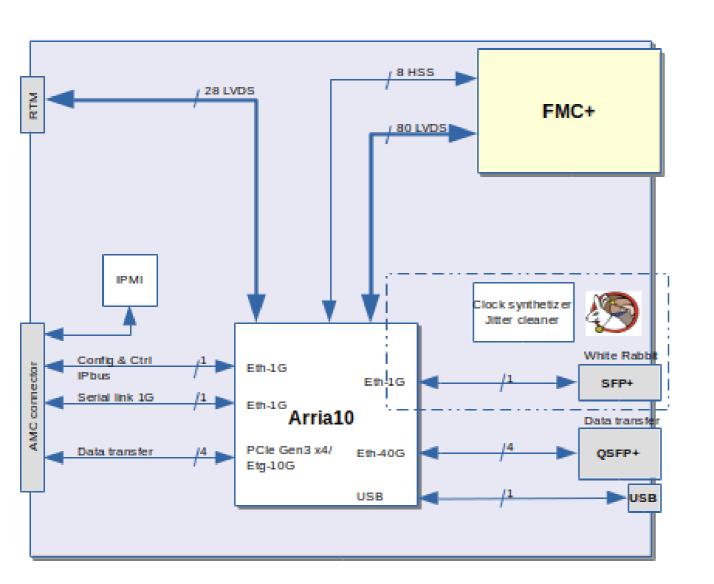

- MTCA 4.0 standard, double width full-size

- Stand-alone mode

- VITA57.1 (FMC slot)

- 160 single-ended I/Os (80 LVDS) and/or up to 10 serial transceivers in a 40 x 10 configuration

- Full WhiteRabbit compliant.

- Front panel conectivity

- WR SFP+

- QSFP+ 40G, USB

- Backplane connectivity

- 1Gbe IPbus,PCI 4x Gen3,

- IPMB, CLK & trigger lane.

- RTM connector : J30

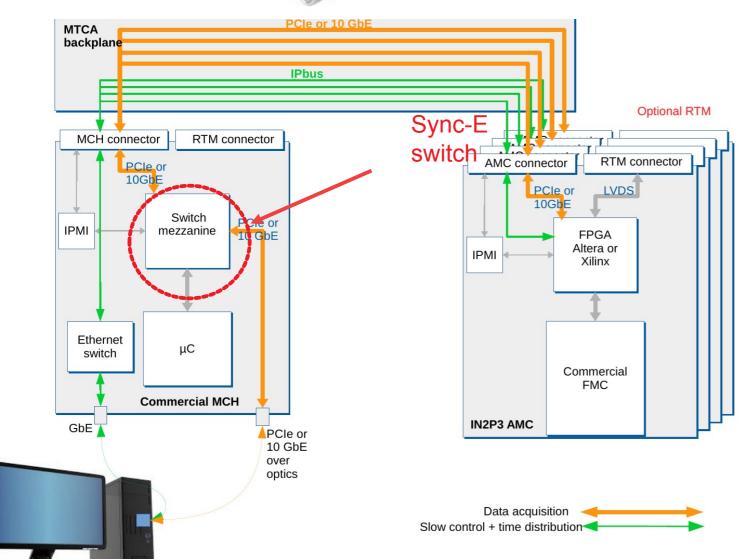

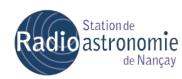

# WhiteRabbit : DAQGEN implementation

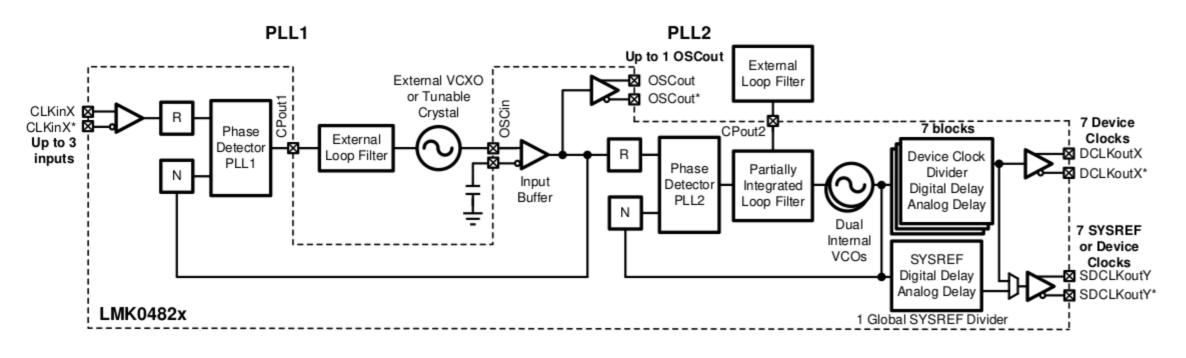

**SFP** Ref clock generator VCXO DAC PHY 125MHz 25MHz **FPLL** LMK04828 VCXO Etherbone **WR PTP** 100Mhz PLL 2 PLL 1 core 125MHz LMK04828 Clock jitter cleaner PLI DMTD 62.5MHz Phase PLI Detetector DMTD clock generator → PLI 125MHz DAC VCXO

http://www.ohwr.org/projects/white-rabbit/wiki/WRReferenceDesign

Systèmes de Référence Temps-Espace

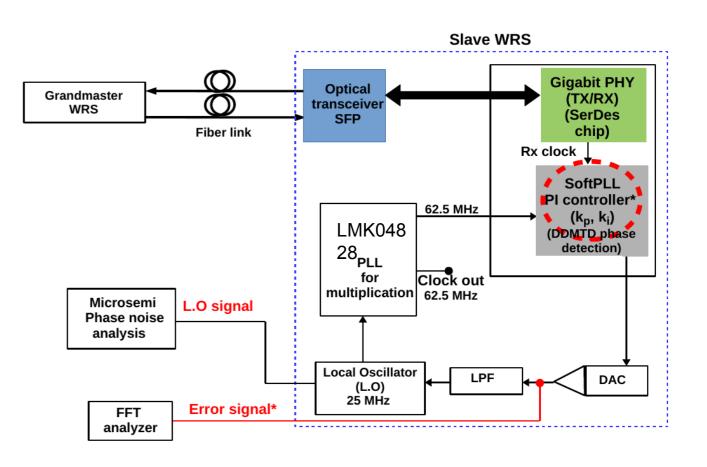

The WhiteRabbit IDROGEN hardware is based on CERN open hardware with Enhancements

- Based on LMK4828 synthetiser

- Ultra low noise clock jitter Cleaner with Dual Loop PLL

- 90fs RMS jitter.

- DDMTD internal of FPGA (placement with constraint)

- Two generated local clocks :

- DDMTD source (comparison between WR master clock from SFP)

- PLL source with phase adjustment

### IDROGEN Enhancements

- PLL selection

- VCXO Frequency

- Input frequency for DDMTD )

- Tx/Rx routing equalisation

# WhiteRabbit, SYRTE test system

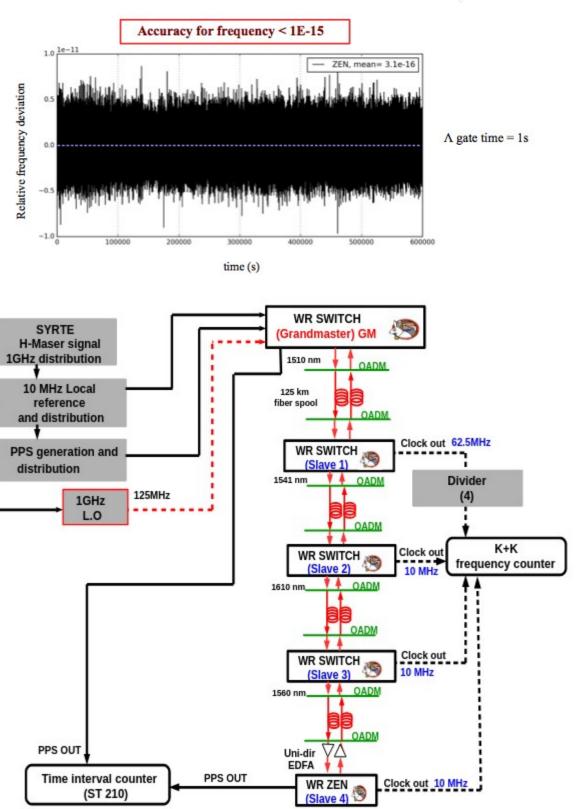

- For the test we use the test system developed by the SYRTE for timing distribution measurement.

- fs measurement capability

- Very high timing stability 10e-16

- WR switch improvement.

- Remove of local PLL

- Conditioned room.

- Dedicated measuring apparatus

- Selection of fiber length

- Selection of transceivers

- IDROGEN version -1

- 400fs after 1000s & 1km of fibers

- Same design as IDROGEN

- IDROGEN system qualificationTest

- With SYRTE test setup

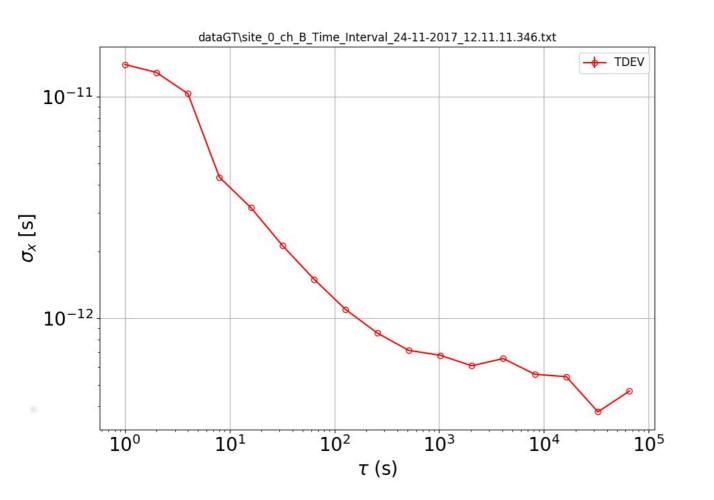

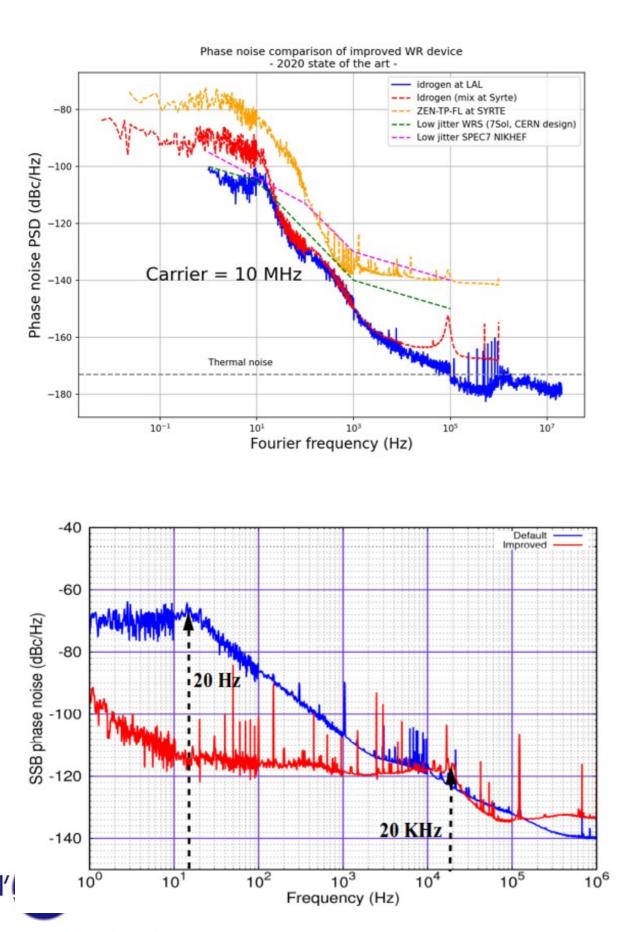

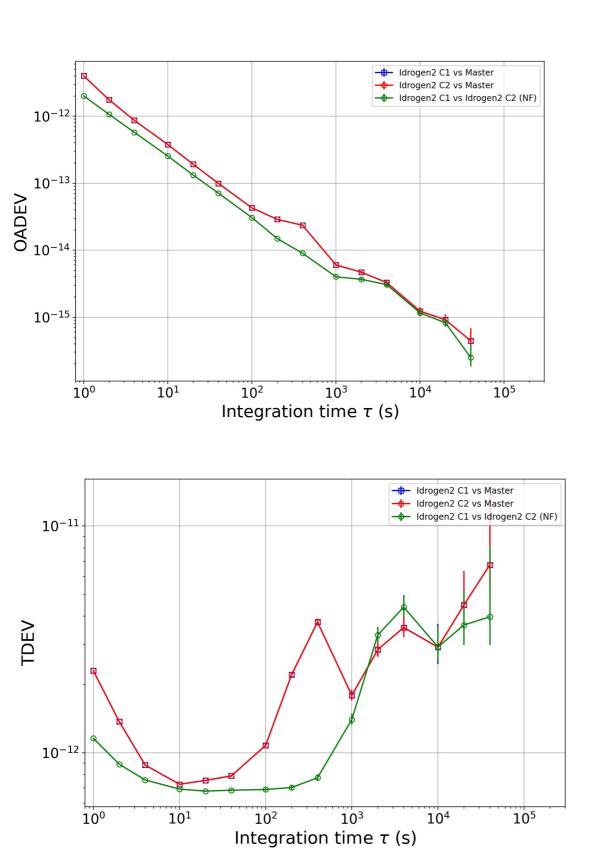

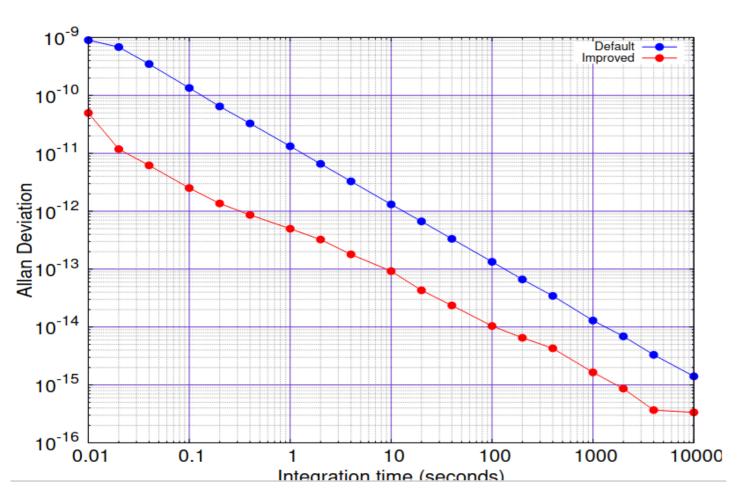

### **NEBULA** performance

- Transfer from one WR switch to two IDROGEN with a short link (few meter)

- For the test we measure the phase difference between 2 nodes (IDROGEN board)

- Best result, one order of magnitude than the « challenger »

- Clock phase jitter

- PPS time precision 1ps RMS

- PPS 2 IDROGEN board

- 25m & 125m of fiber

- ~50ps of dispersion des PPS with calibration

SYRTE

Observatoire

Integration of IPBus and UDP streamer on WR link

- One fiber : Synchro, configuration, data readout

- WR node status on integrated IPbus

# Resarch and technology : TIMED

# Rsearch & Technology : TIMED

- Observatory of Paris & IN2P3 laboratories collaboration

- Extend domain of WhiteRabbit

- WhiteRabbit node simplification of technical integration

- Improvement of WR performance

- Integration of external components by firmware function

- High stability frequencies distribution

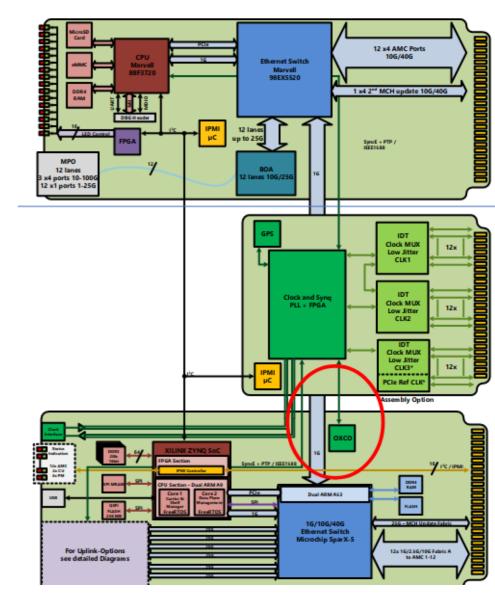

# R & T TIMED 1 : WR Crate integration

- WhiteRabbit on µTCA

- Only switch functionality (no master)

- WhiteRabbit on copper link

- Sync-E function on MCH board

- NAT-MCH-4

- IEEE1588V2 compliant switch

# <u>R & T IMED 2 : Simplification of WR integration</u>

- Replacement of GXB by DDR I/O (up to 800MHz capability)

- IP Native-PHY by IP TSE Pcs only

- Integrated PHY functionality replaced by RTL code

- Integration of external PLL by internal one

# <u>R & T TIMED 3 : Increasing performances</u>

- Collaboration with Paris Observatory Laboratory

- Soft PLL modification

- Decrease the response time of software PLL

- μP upgrading :Replacement of the universal μP based on logic bloc by dedicated μP (NIOS) or hardware μP (SOC)

- Gain integrator optimization

- Increased PLL bandwith of the GM Local oscillator

- Components upgrading

- VCXO selection

- Increase Frequency (reduce PLL number)

# R & T TIMED 4 : Firmware integration

- External PLL integration

- Internal reconfiguration

- µP Software upgrade

- VCXO intégration

- Derived from video IP

- FPGA manufacturer dependent

Application Note: 7 Series FPGAs and Zynq-7000 AP SoCs

### All Digital VCXO Replacement for Gigabit Transceiver Applications (7 Series/Zynq-7000)

Authors: David Taylor, Matt Klein, and Vincent Vendramini

#### Summary

stèmes de Référence Temps-Espace

This application note delivers a system that is designed to replace external voltage-controlled crystal oscillator (VCXO) circuits by utilizing functionality within each serial gigabit transceiver.

Note: In this application note, transceiver refers to these types of transceivers:

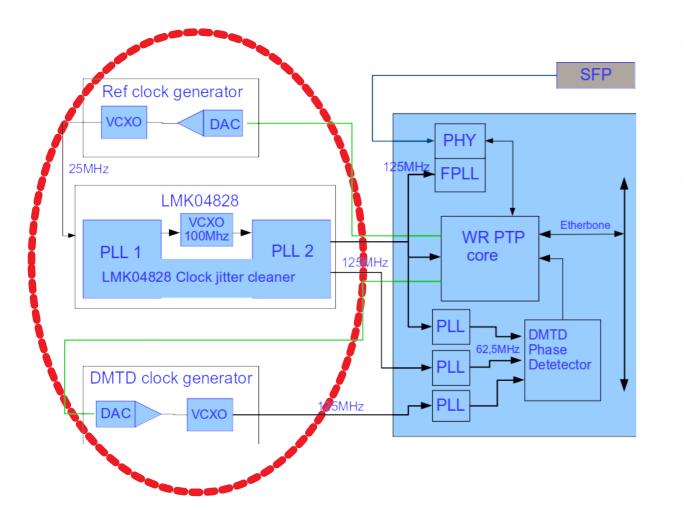

# <u>R & T TIMED 5 : High stability frequency distribution</u>

- Implementation of a synthesizer on mezzanine FMC : SI5395

- Collaboration with accelerator department

- Design mid 2023

- Phase jitter 90 fs

- Frequency : 1kHz < F < 1GHz

- RF filter : outside

Systèmes de Référence Temps-Espace

de Physique des 2 infinis

Irène Joliot-Curie

# **T+RFIMEVE**

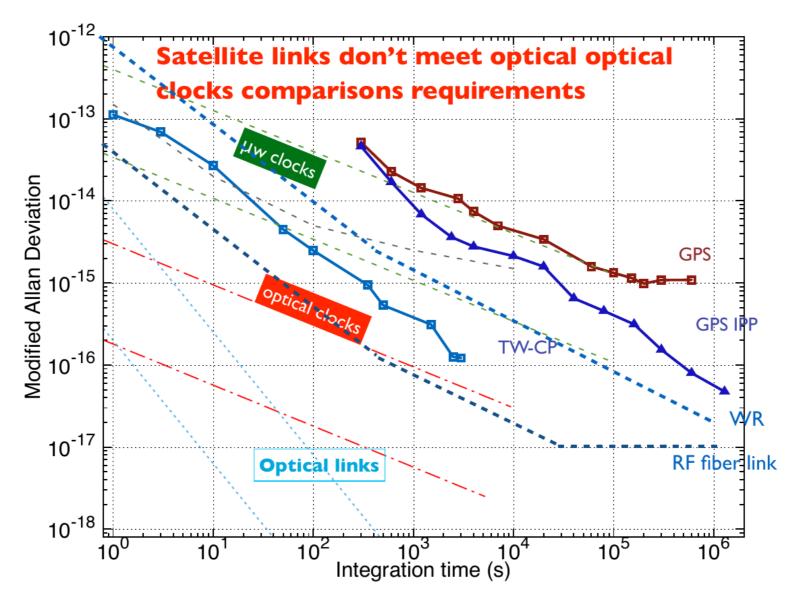

### **Overview of comparison methods**

| WitteRabbit                  | Stabilité 1s | Stabilité 1j |

|------------------------------|--------------|--------------|

| LAN with commercial hardware | 1e-11        | 1e-13        |

| National network RENATER     | 1e-12        | 1e-15        |

| Development IJCLAB           | 1e-13        | 1e-16        |

Laboratoire de Physique des **2 infinis**

Irène Joliot-Curie

Systèmes de Référence Temps-Espace

SYRTE

bservatoire

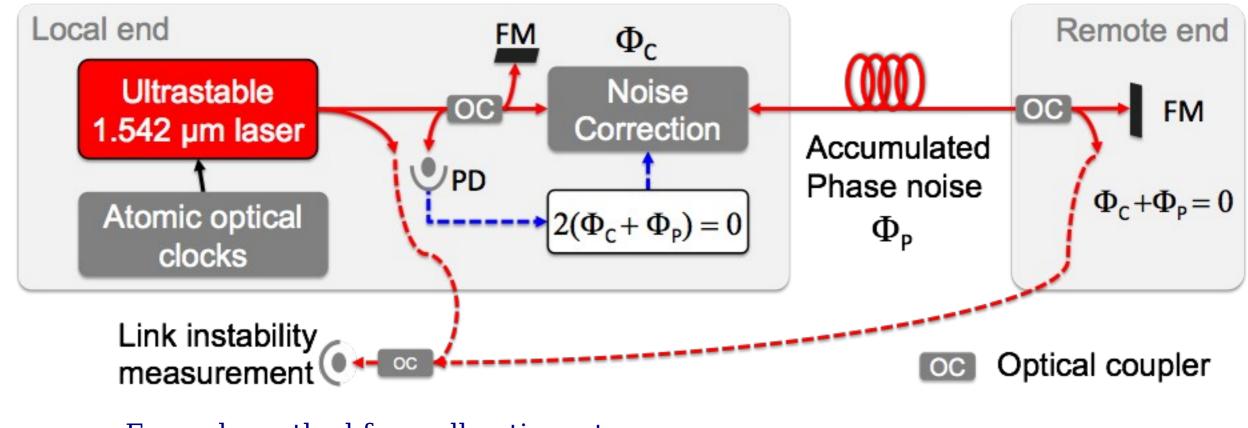

# Problematic : comparison method/ dissemination

- Seminal works: Primas et al, Proc 20<sup>th</sup> PTTI, 1988, Ma et al., OL 1994

- Active noise compensation after one round-trip

- Strong hypothesis : noises forth and back are the same

- 2 ends at the same place (for link stability measurement)

Example method for « all optic system »

Systèmes de Référence Temps-Espace

les 2 infinis

Irène Joliot-Curie

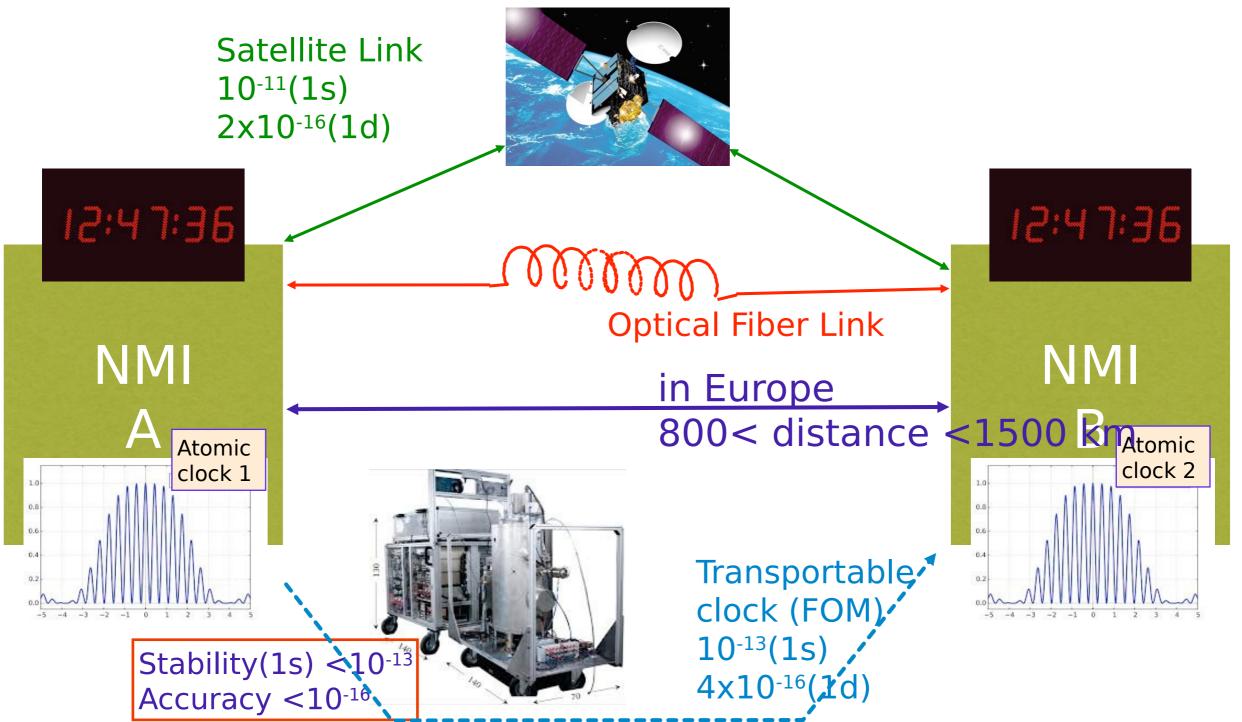

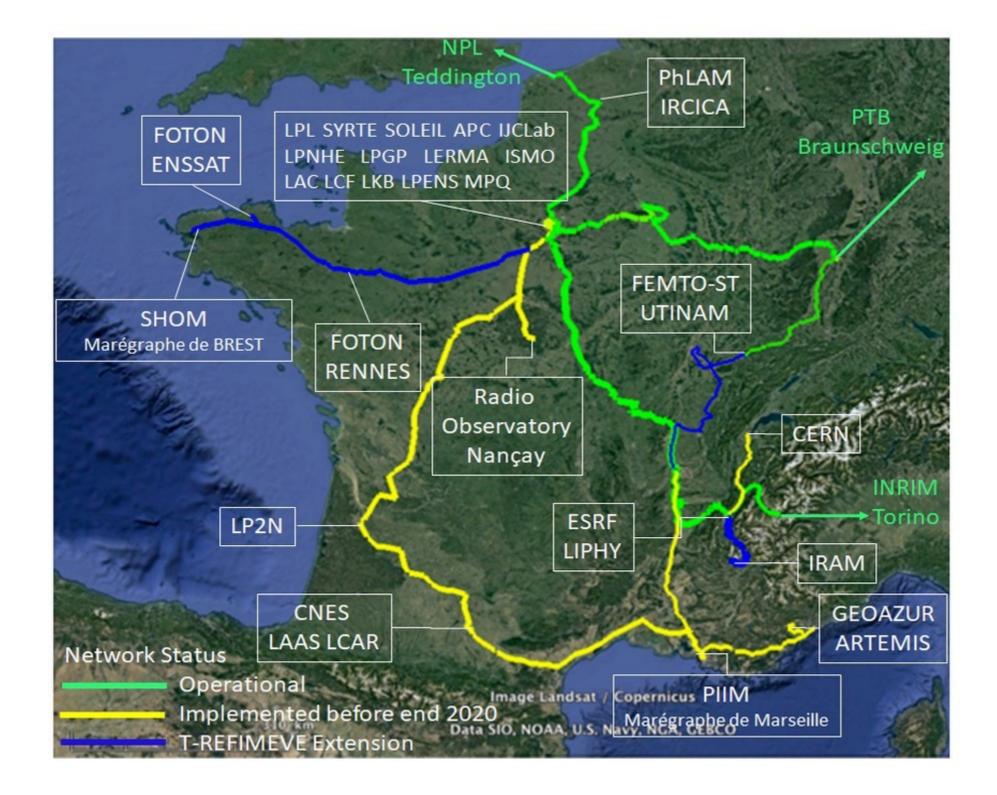

# The requirements of the dissemination of T/F by fiber

#### Frequency metrology:

Access to ultra precise reference frequencies for remote user.

Spectroscopy, photonics, quantum sensors, quantum telecom., ...

#### **Applied dimensional measurements:**

Traceability of the unit of length for interferometric measurements.

#### **Astronomy:**

Phase traceable signals for the synchronization of radio telescopes VLBI, NOEMA, SKA, LOFAR ...

#### **Broadband communication technology:**

Provision of reference signals with low-jitter for synchronization

#### Large research infrastructures

(ESA, DESY, CERN, GSI):

Time and frequency dissemination in ground stations

Industry : wireless, optical telecom. Galileo GNSS ground segment

Irène Joliot-Curie

### Map of REFIMEVE netwok

# **Distributed signals on REFIMEVE netwok**

| Signal provided                    | by T-REFIMEVE                                        | Stability | Stability           | Uncertainty |                 |  |

|------------------------------------|------------------------------------------------------|-----------|---------------------|-------------|-----------------|--|

|                                    |                                                      | @1s       | @lday               | routine     | dedicated       |  |

| Radiofrequency                     | 1 <sup>st</sup> pillar - 10<br>MHz (White<br>Rabbit) | 10-12     | 10-15               | 10-14       | 10-15           |  |

|                                    | 2 <sup>nd</sup> pillar - 1 GHz                       | 10-13     | 3×10 <sup>-16</sup> | 10-14       | 2×10-16         |  |

| Time                               | 1 <sup>st</sup> pillar (White<br>Rabbit)             | 1 ns      | 1 ns                | 10 ns       | 10 ns           |  |

|                                    | 2 <sup>nd</sup> pillar                               | 20-50 ps  | 500 ps              | 10 ns       | 2ns to<br>100ps |  |

| Optical                            | Today                                                | 10-15     | 3×10 <sup>-16</sup> | 10-14       | 2×10-17         |  |

| frequency (194,5<br>THz - 1542 nm) | Expected<br>progress in 5<br>years                   | 10-16     | 2×10 <sup>-17</sup> | 10-14       | 10-18           |  |

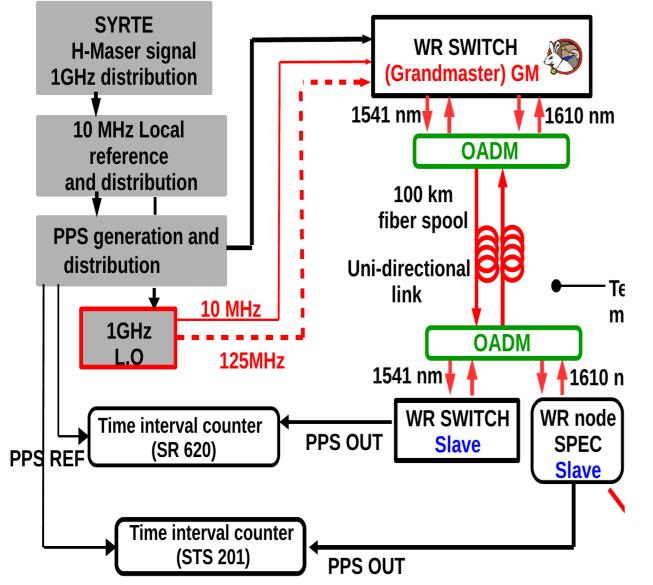

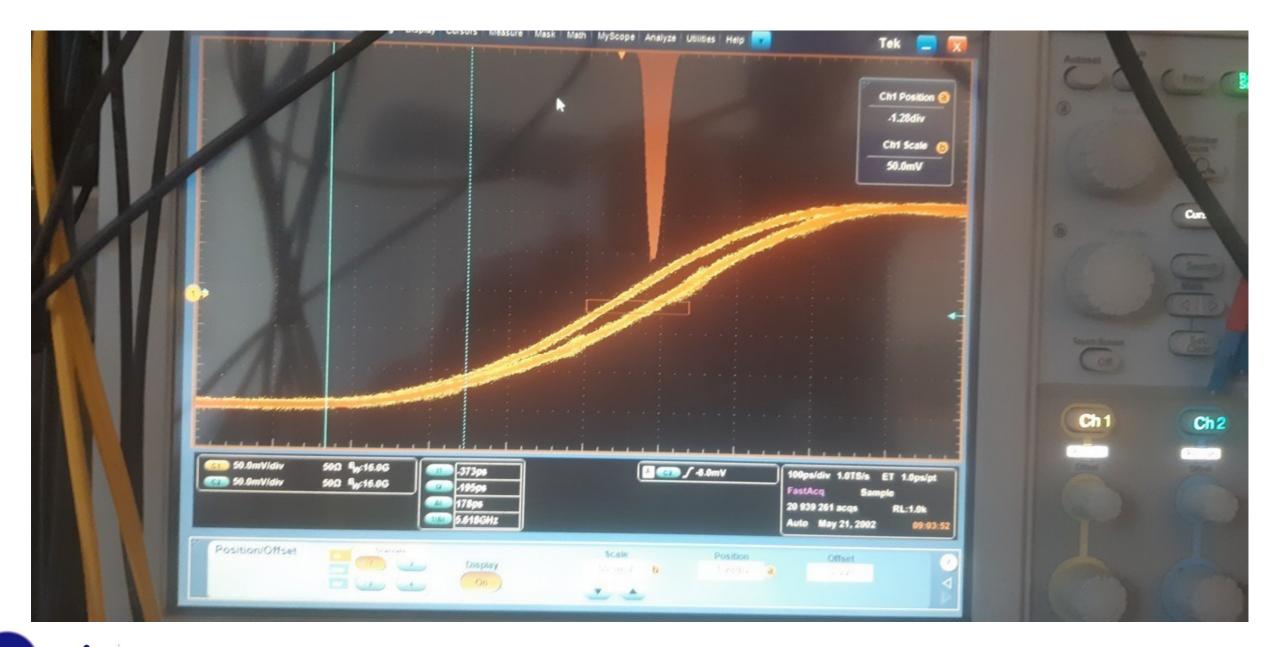

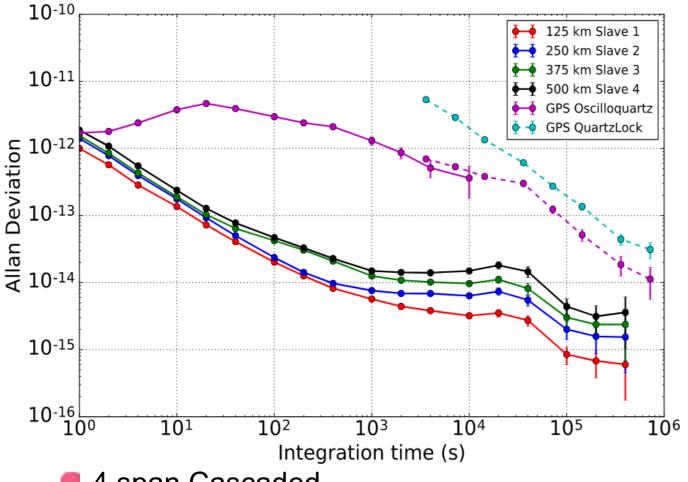

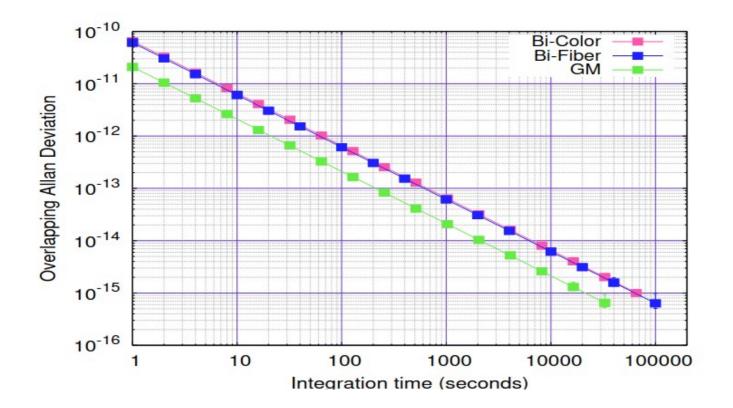

# WR performance on long distance test

4 span Cascaded

- Better than Oscilloquartz GPS receiver

- 500Km (4 x 125Km) of fiber

- 🗖 Uni-dir fiber

SYRTE

bservatoire

- 2 OADM (multi wavelength)

- Fiber noise become dominant with the length

- System disparity, reciprocity of the link

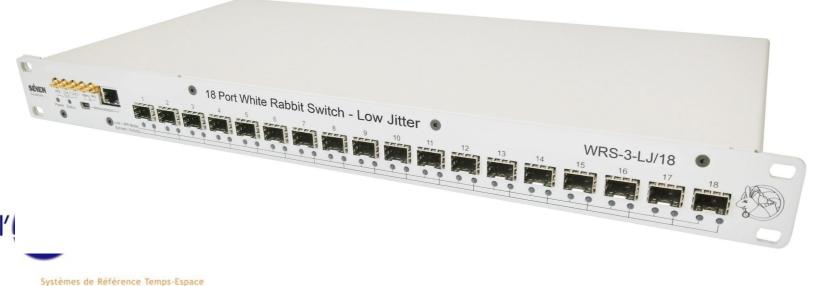

- WR switch

- Low jitter WRS-3-LJ/18

- WRS-3/18

- Scope

- 100G samples 17GHz of bandwith

- T+REFIMEVE node at the laboratory

- Phase meter

- IDROGEN board

- The WR is a very efficient system to distribute high stability frequency and very precise time stamping

- It is currently being standardized by IEEE (1588-V2)

- The WR allows to distribute very precise time on distance up to 1000km

- Time stamping for long base line radio-telescope

- Multi-messenger physics

- On the shelf system

- We will extend the area of use of the WR : R&T TIMED (implementation,stability,...)

- The WR allows the conception of new system architecture.

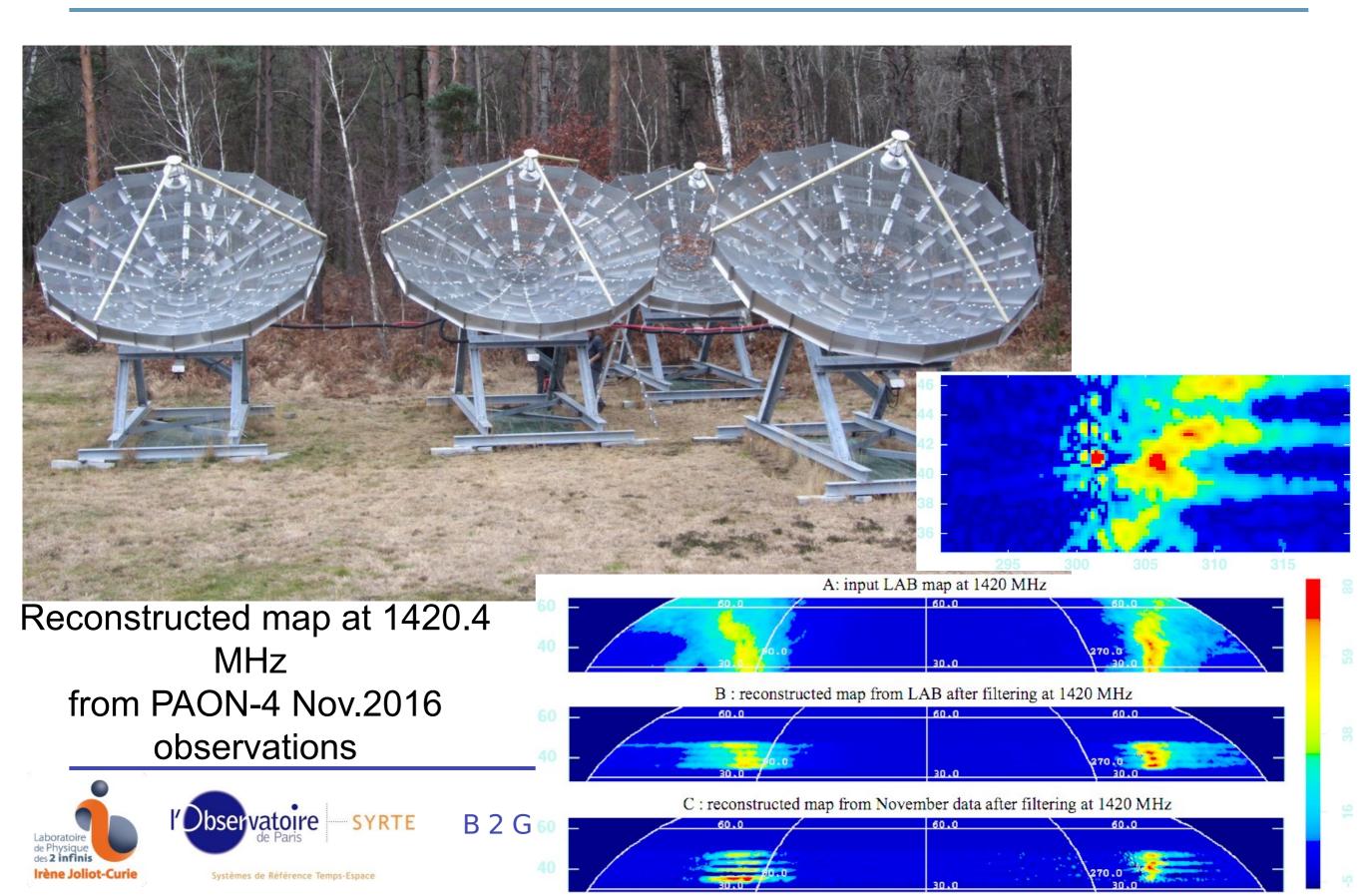

- Ex : distributed high-frequency coding system for radio astronomy detector (PAON IV detector)

- The future of WR will be the upgrade to 10G

- Ongoing development

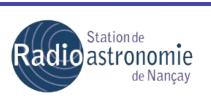

Daniel Charlet on behalf of the R&T PCIe400 team CPPM, IJClab, IP2I, LAPP, LPCC, CERN (LHCb Online)

#### **Foreseen characteristics**

- Agilex7 M-series AGMF039R47A1E2V

- No DDR memory Use of PC RAM or HBM2e instead

- Up to 48x26Gbps NRZ for FE

- PCIe Gen 5 / CXL or 400GbE

- Low jitter PLL < 100 fs RMS</p>

- White Rabbit clock distribution (1ps) (SFP+)

- PON interface for fast control (SFP+)

#### Early Access program granted by Intel

#### **New FPGA ressources**

- Serial links up to 112Gb/s

- HBM / NoC (Network on Chip)

- Facilitate high-bandwidth data movement between core logic and HBM

- Deep learning acceleration

- smartNIC to accelerate and offload certain functions from the server

#### Foreseen gain (compared to PCIe40)

Processing : factor 8 to 12

|                            | PCIe40    | PCIe400                  |

|----------------------------|-----------|--------------------------|

| Family                     | Arria 10  | Agilex7 M-series         |

| Logic elements             | 1.2 M     | 3.9 M                    |

| DSP                        | 1.5 K     | 12 K                     |

| Frequency<br>(silicon max) | 650MHz    | 1GHz                     |

| HBM2e                      | -         | 32GB                     |

| Hard co-<br>processor      | -         | Arm Cortex A53<br>MPCore |

| Package                    | 2000 pins | 4500 pins                |

|                                             |                                            | 20 | 22 |    |                               | 20 | 23      |        |    | 20 | 24 |    |

|---------------------------------------------|--------------------------------------------|----|----|----|-------------------------------|----|---------|--------|----|----|----|----|

| Task                                        | Q1                                         | Q2 | Q3 | Q4 | Q1                            | Q2 | Q3      | Q4     | Q1 | Q2 | Q3 | Q4 |

| Design                                      |                                            |    |    | 1  |                               |    |         |        |    |    |    |    |

| Placing & Routing                           |                                            |    |    |    |                               |    |         |        |    |    |    |    |

| Manufacturing                               |                                            |    |    |    |                               |    | 1       |        |    |    |    |    |

| Definition unitary tests                    |                                            |    |    |    |                               |    |         |        |    |    |    |    |

| Implementation of unitary tests             |                                            |    |    |    |                               |    |         |        |    |    |    |    |

| Prototype Debug                             |                                            |    |    |    |                               |    |         |        |    |    |    |    |

| <b>Qualification &amp; Characterization</b> |                                            |    |    |    |                               |    |         |        |    |    |    |    |

|                                             |                                            |    |    |    | Prototype available July 2023 |    |         |        |    | 23 |    |    |

|                                             | Routing review internal and Intel Mar      |    |    |    |                               |    | rch 202 |        |    |    |    |    |

|                                             | Schematics review internal and Intel Janua |    |    |    |                               |    | Januar  | y 2023 |    |    |    |    |

- Important design effort on power estimation and thermal simulations

- As of today, schematics are done

### <u>Synthesis</u>

#### IN2P3 R&D

- Project set up to develop the prototype of PCIe40 next generation

- Design a generic readout DAQ for muti context use

- Interest from several collaborations (LHCb, Alice and CTA)

- Funded for 3 years from 2022 to end of 2024

#### **Technical challenges to tackle**

- Power distribution >100A for FPGA core in a 18 layers PCB

- Cooling solution for FPGA and optical transceivers

- High speed serial interface routing up to 112Gb/s

- Network interface on board through 400GbE (experimental)

- Use of on-Chip ressources to embed neural network for processing acceleration

#### Project follow up

Discussions with IN2P3 are on-going to envisage a production at the horizon of 2026-2028

# Backup

PAON IV

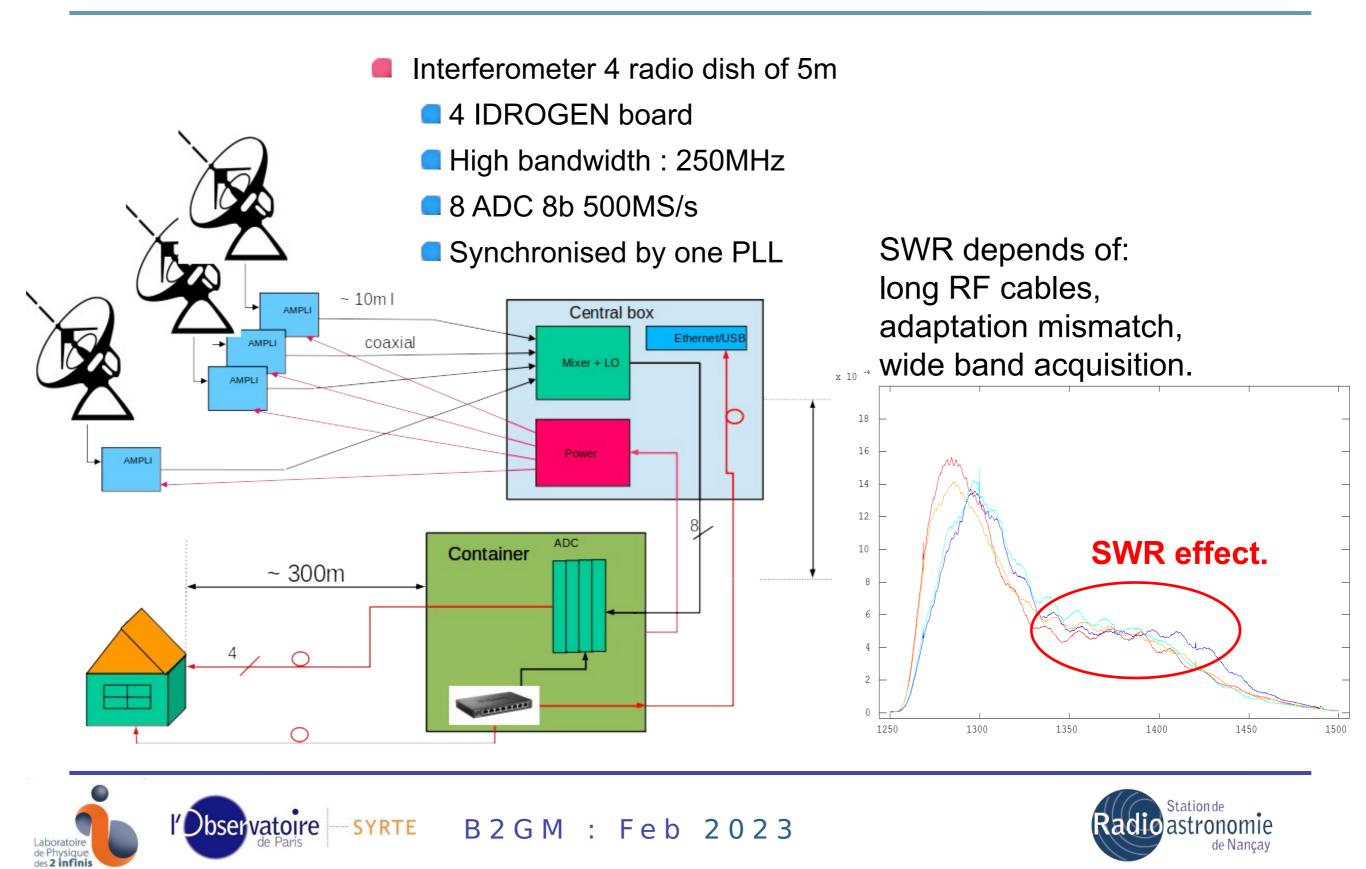

### **PAON IV**

### **PAON IV : Current configuration**

Systèmes de Référence Temps-Espace

Irène Joliot-Curie

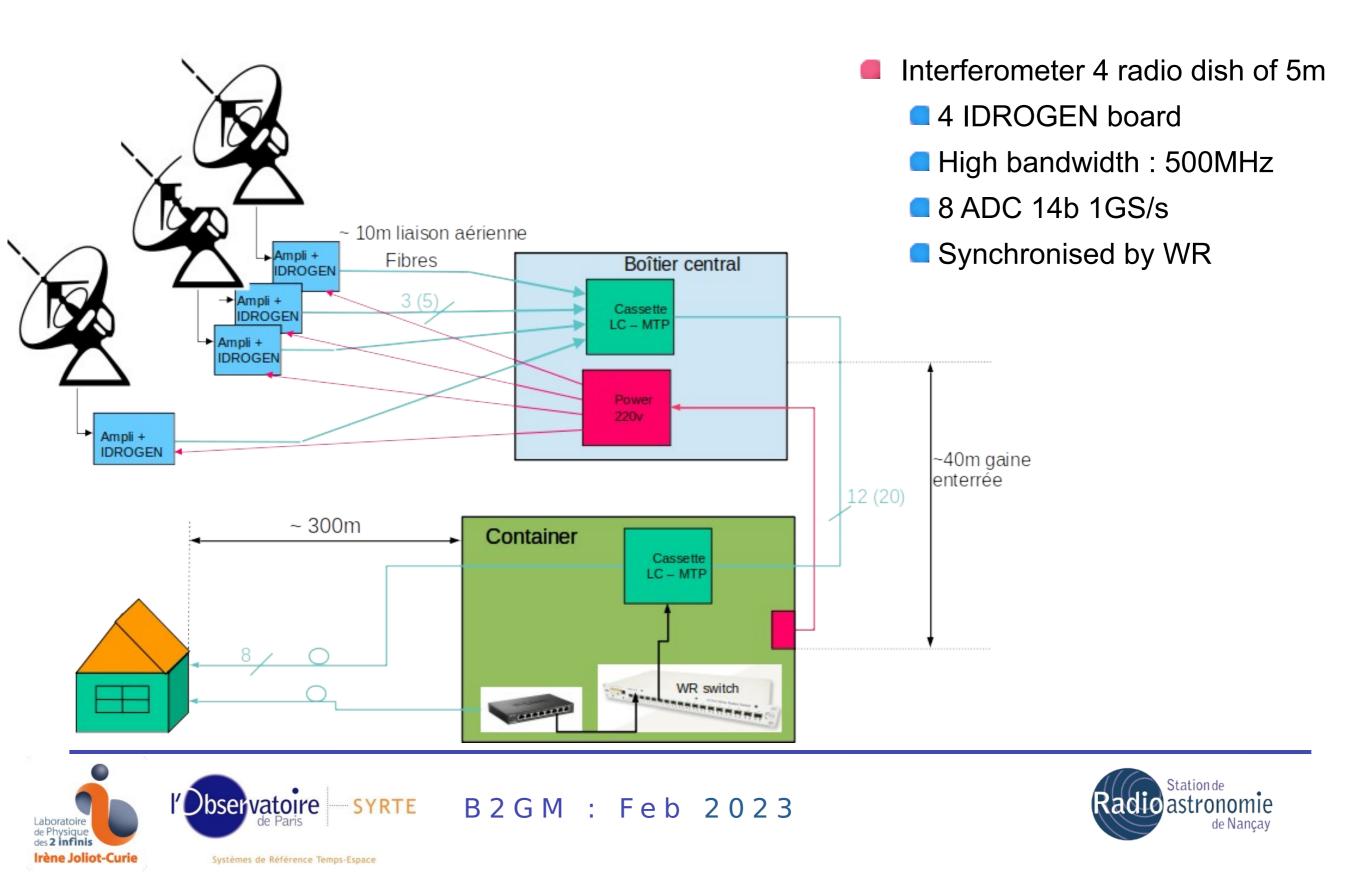

### **PAON IV : Future configuration**

### IDROGEN + mezzanine ADC

### Backup

### **IDROGEN** preliminary measurements

For the test we measure the phase difference between 2 nodes (IDROGEN board)

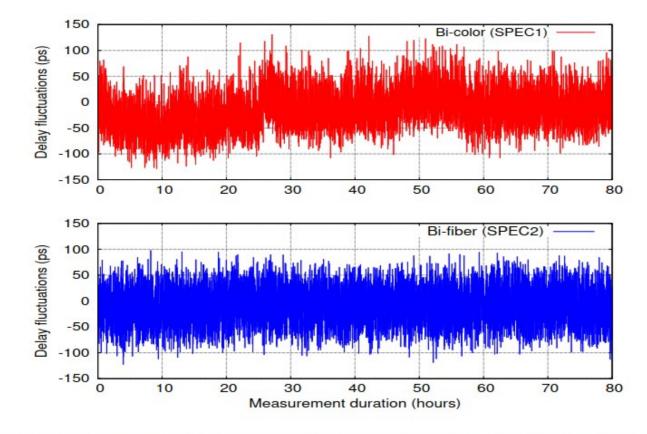

### Fibers comparaison

FIGURE 3.15: Phase data for the uni-directional (Bi-fiber) and bidirectional (Bi-color) setups.

- Increased PLL bandwith of the GM Local oscillator

- Better clocking scheme

- Better choice of components

- Decrease reponse time of the software PLL

### **IDROGEN Clock generator : LMK04828**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LMK04828B R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | gisters                                                                               | T |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---|

| LMK04828B register set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Reg0x15D = 00                                                                         |   |

| Reset FPGA Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Read Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Receive Reg0x15E = 00<br>Reg0x15F = 0B                                                |   |

| nput clock PLL1 summary PLL1 OSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Out PLL2 summary PLL2 SYSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reg0x160 = 00           Reg0x161 = 01           Reg0x162 = 24           Reg0x163 = 00 |   |

| Clock group select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DCLKout 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reg0x164 = 00<br>Reg0x165 = 00                                                        |   |

| Cucker Power Source Sou | Divider DYN DDLY CNT<br>24 2 2 2<br>DDLY CNTL DYN DDLY CNT<br>16 2 2 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reg0x167 = 00<br>Reg0x168 = 0F                                                        |   |

| OCLKout 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DDLY CNTH Dynamic DDLY<br>Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Reg0x16C = 00<br>Reg0x16D = 00<br>Reg0x16E = 13                                       |   |

| Power Down MUX ADLY (ps) DDLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MUX Polarity<br>Divider on!  Normal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MHz Reg0x171 = AA<br>Reg0x172 = 02<br>Reg0x173 = 00                                   |   |

| Device cl 💌 🚺 🚔 Bypass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | → ADLY MUX ADLY (ps)<br>Without du → 0 ps →                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Reg0x174 = 00<br>Reg0x17C = 15                                                        |   |

| Output mode         Output format         Polarity           Active in *         Power Down *         Normal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Output format     LVDS     The second s | Reg0x17D = 33<br>Reg0x182 = 00<br>Reg0x183 = 00                                       |   |

| Half shift ADLY Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>✓ DDLY PD</li> <li>✓ ADLY PD</li> <li>✓ ADLYg PD</li> <li>✓ HSg PD</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reg0x184 = 00<br>Reg0x185 = 00<br>Reg0x188 = 00<br>Reg0x1FFD = 00                     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Half shift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reg0x1FFE = 00<br>Reg0x1FFF = 53                                                      |   |

### LMK04828

- Frequency programmable 80MHz to 3 Ghz

- Analog delay adjusment by 25ps step

- ~ 100fs rms jitter

- JESD20B compatible

- Free runinng or synchro WR

- Configure by µP.

- Re-configuration by USB or Eth

- Output clk on sma connector